# The STAR Heavy Flavor Tracker Conceptual Design Report

Date: November 4, 2009

# A Heavy Flavor Tracker for STAR

D. Beavis, R. Debbe, J.H. Lee, M.J. LeVine, R.A. Scheetz, F. Videbaek, Z. Xu Brookhaven National Laboratory, Upton, NY 11973

J. Bielcik, M. Krus Czech Technical University, 115 19 Prague, Czech Republic

L.E. Dunkelberger, H.Z. Huang, S. Sakai, G. Wang, C. Whitten Jr. University of California, Los Angeles, CA 90095

J. Bouchet, J. Joseph, D. Keane, S. Margetis, V. Rykov, J. Vanfossen, W.M. Zhang Kent State University, Kent, OH 43210

J. Kapitan, V. Kushpil, M. Sumbera Nuclear Physics Institute AS CR, 250 68 Rez/Prague, Czech Republic

> G.Visser Indiana University Cyclotron Facility Bloomington, IN 47408

J. Baudot, A. Brogna, G. Claus, R. De Masi, A. Dorkhov, G. Doziere, W. Dulinski, M. Goffe, A. Himmi, C. Hu-Guo, F. Morel, A. Shabetai, M. Winter, I. Valin, G. Voutsinas Institut Pluridisciplinaire Hubert Curien, Strasbourg, France

J. Bessuille, B. Buck, D. Hasell, J. Kelsey, R. Milner, R. Redwine, B. Surrow, G. Van Nieuwenhuizen, S. Steadman Laboratory for Nuclear Science Massachusetts Institute of Technology, Cambridge, MA 02139

E. Anderssen, X. Dong, L. Greiner, F-X. Luo, H. Masui, H.S. Matis, H.G. Ritter, E. Sichtermann, T. Stezelberger, X. Sun, M. Szelezniak, J.H. Thomas, C. Vu, H.H. Wieman, N. Xu, Y. Zhang Lawrence Berkeley National Laboratory, Berkeley, CA 94720

A. Hirsch, X. Li, B. Srivastava, F. Wang, W. Xie Purdue University, West Lafayette, IN 47907

S. Bouvier, B. Erazmus, A. Geromitsos, G. Guilloux, S. Kabana, C. Renard SUBATECH – Ecole des Mines, Nantes, France

G.W. Hoffmann, J.J. Schambach University of Texas, Austin, TX 78712

# **Table of Content**

| 1. | INTRO            | ODUCTION                                       | 12 |

|----|------------------|------------------------------------------------|----|

| 2. | PHYSI            | ICS MOTIVATION                                 | 13 |

|    | 2.1. An          | NALYSIS PROCEDURE                              | 14 |

|    |                  | MESONS                                         |    |

|    | 2.3. PE          | REFORMANCE OF ALTERNATE CONFIGURATIONS         |    |

|    | 2.3.1.           | System Performance without SSD or IST          |    |

|    | 2.3.2.           |                                                |    |

|    |                  | harm Flow                                      |    |

|    |                  | EAVY QUARK ENERGY LOSS                         |    |

|    | 2.6. $\Lambda_0$ | g-Baryons                                      |    |

|    | 2.6.1.           |                                                |    |

|    | 2.6.2.           | Simulation Procedure                           |    |

|    | 2.6.3.           |                                                |    |

|    | 2.6.4.           | •                                              |    |

|    |                  | MESONS                                         |    |

|    | 2.7.1.           | , 8                                            |    |

|    | 2.7.2.           |                                                |    |

|    | 2.7.3.           |                                                |    |

|    |                  | PRODUCTION AT MID-RAPIDITY                     |    |

|    | 2.8.1.           | Mid-rapidity W Program at STAR                 |    |

|    | 2.8.2.           | Electron/Hadron Separation at Mid-rapidity     |    |

|    | 2.8.3.           | Charge-sign Discrimination at Mid-rapidity     |    |

|    | 2.8.4.           | Projected Performance of W Production          | 41 |

| 3. | FUNC'            | TIONAL REQUIREMENTS                            | 43 |

|    | 3.1. GI          | ENERAL DESIGN CONSIDERATIONS                   | 43 |

|    | 3.2. PC          | DINTING RESOLUTION                             | 44 |

|    | 3.3. M           | ULTIPLE SCATTERING IN THE INNER LAYERS         | 44 |

|    |                  | TERNAL ALIGNMENT AND STABILITY                 |    |

|    |                  | KL Integration Time                            |    |

|    |                  | EADOUT SPEED AND DEAD TIME                     |    |

|    |                  | ETECTOR HIT EFFICIENCY                         |    |

|    |                  | VE CHANNELS                                    |    |

|    | 3.9. Sc          | OFTWARE AND PROCEDURES READY                   | 46 |

| 4. | TECH             | NICAL DESIGN                                   | 47 |

|    | 4.1. RE          | EQUIREMENTS AND DETECTOR DESIGN                | 47 |

|    | 4.2. TH          | HE PIXEL DETECTOR (PXL)                        | 49 |

|    | 4.2.1.           | Technology Choice                              | 50 |

|    | 4.2.2.           | Design Considerations                          |    |

|    | 4.2.3.           | Mechanical Design of the PXL Detector          | 53 |

|    | 4.2.4.           | Sensors and Readout                            | 61 |

|    | 4.2.5.           | Sensors and Readout Simulation and Prototyping |    |

|    | 4.2.6.           | Engineering Prototype                          |    |

|    |                  | HE INTERMEDIATE STAR TRACKER                   |    |

|    | 4.3.1.           | Requirements                                   |    |

|    | 4.3.2.           | Design Choices                                 |    |

|    | 4.3.3.           | The Silicon Pad Sensors                        |    |

|    | 4.3.4.           | The Readout Chips                              |    |

|    | 4.3.5.           | Hybrids and Modules                            | 80 |

| 4.3.6.           | Mechanical Support Structure                 |     |

|------------------|----------------------------------------------|-----|

| 4.3.7.           | Cooling                                      | 84  |

| 4.3.8.           | Readout System and DAQ Interfacing           | 84  |

| 4.3.9.           | Slow Controls System                         |     |

| 4.3.10.          |                                              |     |

|                  | E SILICON STRIP DETECTOR                     |     |

| 4.4.1.           | The SSD Barrel                               |     |

| 4.4.2.           | Electronic Upgrade                           |     |

| 4.4.3.           | Mechanical Mounting                          |     |

| 4.4.4.           | Cooling System                               |     |

| 4.4.4.<br>4.4.5. | SSD Ladder Status                            |     |

|                  |                                              |     |

| 4.4.6.           | Rack Space                                   |     |

| 4.4.7.           | Services                                     |     |

|                  | OBAL SUPPORT                                 |     |

| 4.5.1.           | Mechanical Supports and Structures           |     |

| 4.5.2.           | Assembly Sequence                            |     |

| 4.5.3.           | Beam Pipe                                    |     |

|                  | FTWARE                                       |     |

| 4.6.1.           | STAR Software Environment                    |     |

| 4.6.2.           | Online Software                              |     |

| 4.6.3.           | Offline Software                             | 113 |

| 4.6.4.           | Simulation Framework                         | 116 |

| 4.6.5.           | Physics Analysis Framework                   | 119 |

| 4.6.6.           | Institutional Responsibilities               |     |

| 5. MANA          | GEMENT                                       | 121 |

| 5.1. MA          | ANAGEMENT ORGANIZATION AND RESPONSIBILITIES  | 121 |

| 5.1.1.           | Department of Energy                         |     |

| 5.1.2.           | Brookhaven National Laboratory               |     |

| 5.1.2.<br>5.1.3. | BNL Contractor Project Manager               |     |

| 5.1.4.           | Engineering Deputy                           |     |

| 5.1.4.<br>5.1.5. | 0 1 ,                                        |     |

| 5.1.5.<br>5.1.6. | Subsystem Managers                           |     |

| 5.1.0.<br>5.1.7. | Quality Assurance Board                      |     |

|                  | Project Integrator(s)                        |     |

|                  | TEGRATED PROJECT TEAM                        |     |

|                  | RTICIPATING INSTITUTIONS                     |     |

|                  | ST AND SCHEDULE                              |     |

|                  | HEDULE                                       |     |

|                  | LESTONES                                     |     |

| 5.7. Co          | ST SCOPE                                     | 129 |

| 5.7.1.           | Contingency                                  |     |

| 5.8. ES          | &H/ QA                                       | 130 |

| 5.8.1.           | Integrated Safety Management                 |     |

| 5.8.2.           | NEPA                                         |     |

| 5.8.3.           | ESSH Plans for Construction and Installation |     |

|                  | OJECT QUALITY ASSURANCE PROGRAM              |     |

| 6. ACRO          | NYMS                                         | 133 |

| 7. APPEN         | DIX 1                                        | 134 |

| 7.1. Mi          | ECHANICAL DESIGN SIMULATION AND ANALYSIS     | 134 |

| 7.1.1.           | Ladder Support Structural Analysis           |     |

| 7.1.2.           | Ladder Cooling Analysis                      |     |

|                  | ·                                            |     |

|                  | IDIX 2                                       |     |

| 8.1. DE          | SCRIPTION OF THE PXL RDO SYSTEM              | 146 |

|    | 8.1.1.  | Phase-1 Readout Chain             |     |

|----|---------|-----------------------------------|-----|

| 9. | APPEN   | NDIX 3                            | 153 |

|    | 9.1. LV | /DS DATA PATH TESTING DISCUSSION  |     |

|    |         | Hardware                          |     |

|    | 9.1.2.  | Firmware and Software             |     |

|    | 9.1.3.  | Operation of the LVDS Test System |     |

|    | 9.1.4.  | Results                           |     |

| RI | EFERENC | CES                               | 159 |

# **List of Figures**

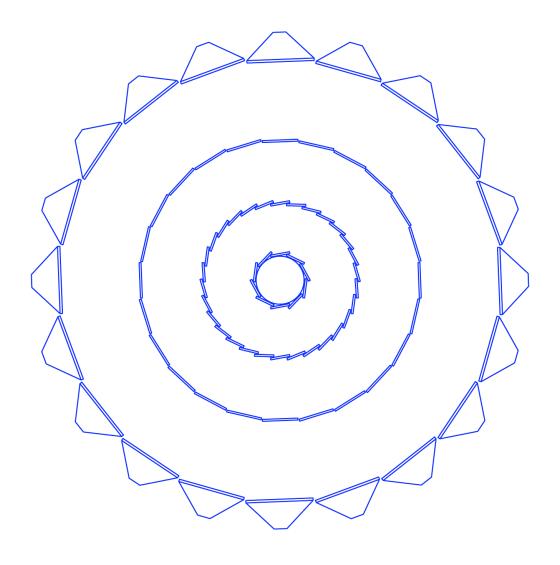

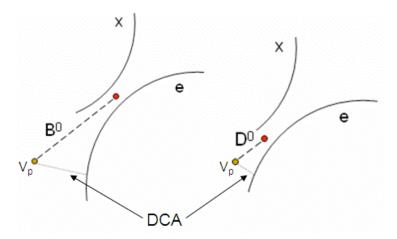

| FIGURE 1: TOPOLOGY OF D <sup>0</sup> DECAY AND CUT VARIABLE DEFINITION                                                        | 16 |

|-------------------------------------------------------------------------------------------------------------------------------|----|

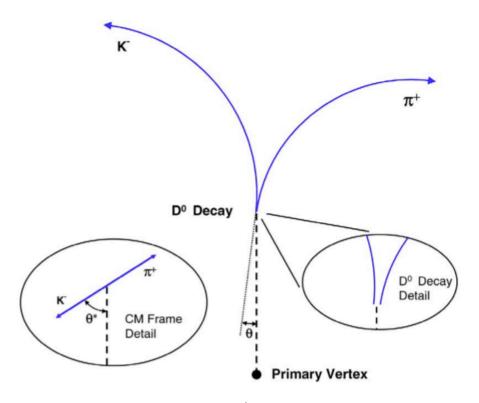

| FIGURE 2: ESTIMATED $D^0$ INVARIANT MASS DISTRIBUTIONS FOR TWO $P_T$ INTERVALS. THE ESTIMATE WAS                              |    |

| BASED ON SIMULATIONS WITH 10 K EVENTS AND DEPENDS ON THE SPECIFIC VALUES OF                                                   |    |

| RECONSTRUCTION CUTS.                                                                                                          | 17 |

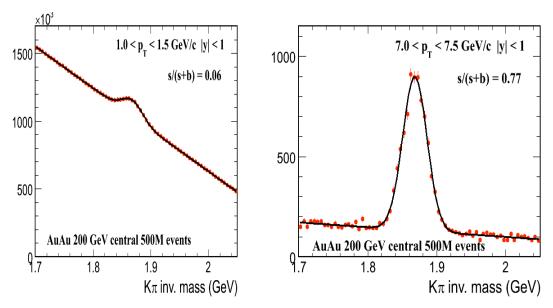

| FIGURE 3: D <sup>0</sup> RECONSTRUCTION EFFICIENCY AS A FUNCTION OF P <sub>T</sub> . FILLED SYMBOLS ARE FOR A POWER LA        |    |

| INPUT DISTRIBUTION AND OPEN SYMBOLS ARE FOR A FLAT (IN P <sub>T</sub> ) INPUT DISTRIBUTION                                    | 17 |

| FIGURE 4: D <sup>0</sup> RECONSTRUCTION SIGNIFICANCE AS A FUNCTION OF P <sub>T</sub> . FILLED CIRCLES ARE FOR A POWER         |    |

| LAW DISTRIBUTION AND OPEN CIRCLES ARE FOR A FLAT DISTRIBUTION.                                                                | 18 |

| FIGURE 5: ESTIMATED STATISTICAL ACCURACY FOR RECONSTRUCTED D <sup>0</sup> SPECTRA. ERRORS SHOWN ARE                           |    |

| STATISTICAL ONLY.                                                                                                             |    |

| FIGURE 6: SINGLE TRACK RECONSTRUCTION EFFICIENCY FOR THE FULL HFT (BLACK), THE HFT WITHOUT                                    |    |

| THE IST (BLUE) AND THE HFT WITHOUT THE SSD (RED) POINTS.                                                                      | 20 |

| FIGURE 7: A MEASURE OF THE SIGNIFICANCE FACTOR FROM SIMULATION FOR THE PXL LAYER WITH A                                       |    |

| RADIATION LENGTH OF $0.32\%$ AND $0.62\%$                                                                                     | 22 |

| Figure 8: Precision projections of the $\mathrm{v}_2$ measurement as a function of $\mathrm{p}_T$ for the case where          |    |

| CHARM FLOWS THE SAME WAY AS LIGHT QUARKS (RED) AND FOR THE CASE WHERE CHARM DOES NOT                                          |    |

| FLOW (GREEN)                                                                                                                  |    |

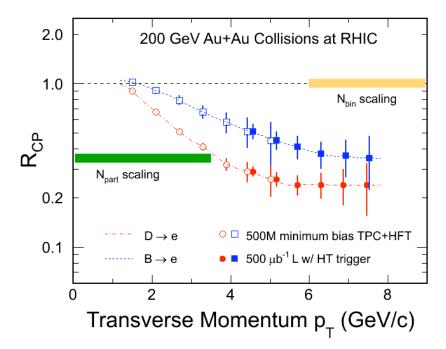

| Figure 9: Expected errors for the $R_{CP}$ measurement as a function of $P_T$ .                                               | 24 |

| FIGURE 10: OPEN CIRCLES SHOW THE PRIMARY VERTEX RESOLUTION IN CENTRAL AU+AU COLLISIONS.                                       |    |

| Solid circles show the $\Lambda_C$ decay vertex resolution. The mean decay distance, $c\tau$ = 59.9                           |    |

| $\mu\text{m},$ for the $\Lambda_{C}$ is shown to guide the eye. Each decay length was scaled by the                           |    |

| APPROPRIATE CT FACTOR TO PROVIDE A UNIVERSAL PEAK FOR THE PURPOSE OF ILLUSTRATION                                             | 26 |

| FIGURE 11: ACCEPTANCE AND EFFICIENCY FOR $\Lambda_C$ RECONSTRUCTION.                                                          | 26 |

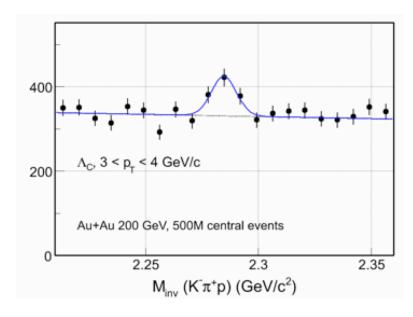

| FIGURE 12: SIMULATED INVARIANT MASS PEAK AND EXPECTED LEVELS OF SIGNAL AND BACKGROUND FOR                                     | }  |

| $P_{T}$ 3-4 GeV/c, in 500 M central Au+Au collisions, assuming no $\Lambda_{C}$ enhancement                                   | 27 |

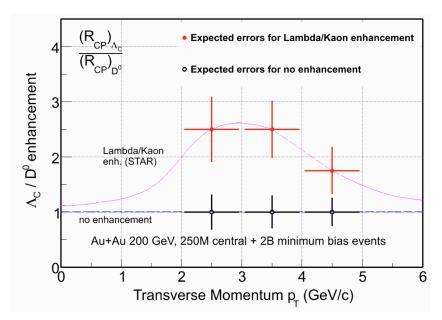

| Figure 13: Statistical errors of the $\Lambda_C/D^0$ ratio for the case of no enhancement and of $\Lambda/K^0_{S'}$           | ;- |

| LIKE ENHANCEMENT.                                                                                                             | 28 |

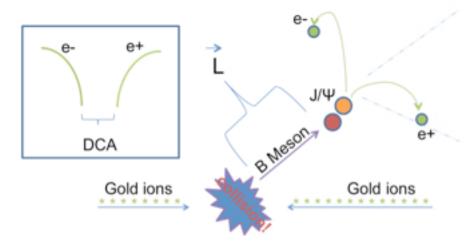

| FIGURE 14: DEFINITION OF VARIABLES USED IN THE ANALYSIS                                                                       | 30 |

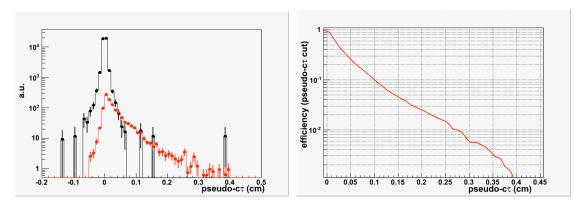

| FIGURE 15: LEFT PANEL: PSEUDO-Cτ DISTRIBUTIONS FOR DIRECT AND B-DECAY J/ψ IN CENTRAL AU+AU                                    |    |

| COLLISIONS AFTER INCLUDING PXL DETECTOR PILE-UP EFFECTS. THE BLACK AND RED HISTOGRAMS                                         | ;  |

| ARE FROM DIRECT AND B-DECAY $J/\psi$ , respectively. The right panel shows the efficiency                                     |    |

| UNDER DIFFERENT PSEUDO-C $	au$ CUTS FOR B-DECAY J/ $\psi$ .                                                                   | 30 |

| FIGURE 16: THE DIFFERENCE OF THE DCA OF DAUGHTER ELECTRONS FROM $D^0$ AND $B^0$ SEMI-LEPTONIC                                 | -  |

| DECAYS.                                                                                                                       | 32 |

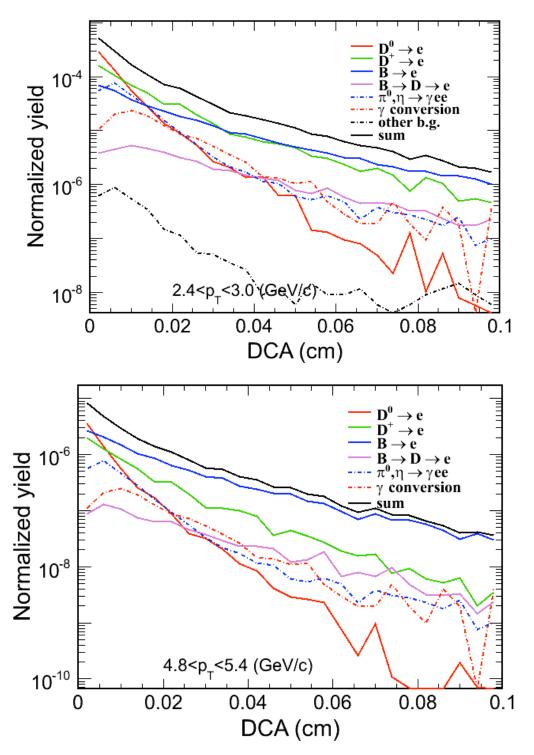

| FIGURE 17: THE ELECTRON DCA DISTRIBUTIONS FOR D AND B MESON SEMI-LEPTONIC DECAY FOR TWO                                       |    |

| DIFFERENT P <sub>T</sub> REGIONS.                                                                                             | 34 |

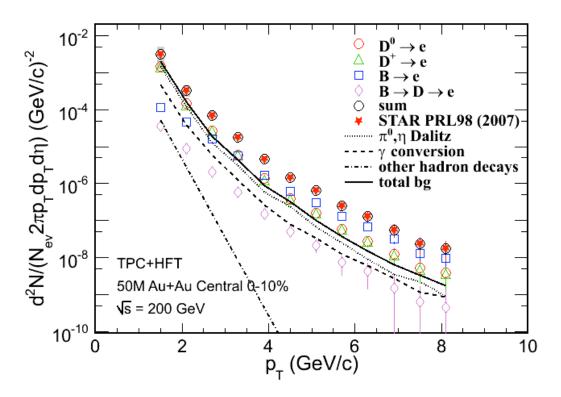

| FIGURE 18: ELECTRON SPECTRA FROM B AND D MESON SEMI-LEPTONIC DECAY. THE EXPECTED ERRORS AS                                    |    |

| A FUNCTION OF P <sub>T</sub> WERE ESTIMATED FOR 50 M AU+AU CENTRAL EVENTS.                                                    | 35 |

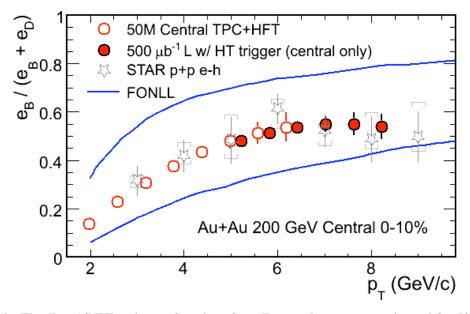

| FIGURE 19: THE ( $B\rightarrow E$ )/NPE RATIO AS A FUNCTION OF $P_T$ . EXPECTED ERRORS ARE ESTIMATED FOR 50 M                 |    |

| AU+AU CENTRAL EVENTS (OPEN CIRCLES) AND 500 μB <sup>-1</sup> SAMPLED LUMINOSITY WITH A "HIGH TOWE                             | R" |

| TRIGGER (FILLED CIRCLES). OPEN STARS REPRESENT PRELIMINARY RESULTS FROM 200 GEV P+P                                           |    |

| COLLISIONS.                                                                                                                   | 35 |

| FIGURE 20: NUCLEAR MODIFICATION FACTOR $R_{CP}$ OF ELECTRONS FROM D MESON AND B MESON DECAYS.                                 |    |

| EXPECTED ERRORS ARE ESTIMATED FOR 500 M AU+AU MINIMUM-BIAS EVENTS (OPEN SYMBOLS) AN                                           | D  |

| 500 μβ <sup>-1.</sup> Sampled luminosity with a "high tower" trigger (filled symbols)                                         |    |

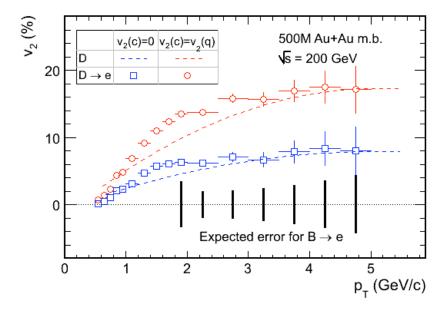

| FIGURE 21: EXPECTED STATISTICAL ERRORS OF D $\rightarrow$ E AND B $\rightarrow$ E V <sub>2</sub> FOR 500 M AU+AU MINIMUM-BIAS |    |

| EVENTS.                                                                                                                       | 37 |

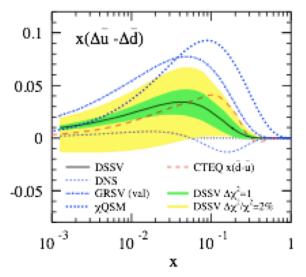

| FIGURE 22: DIFFERENCE OF POLARIZED U-ANTIQUARK AND POLARIZED D-ANTIQUARK DISTRIBUTION                                         |    |

| FUNCTIONS AS A FUNCTION OF X FOR DIFFERENT GLOBAL FIT RESULTS, DSSV, DNS AND GRSV. THI                                        | Ε  |

| RESULT OBTAINED BY THE DSSV FIT IS SHOWN TOGETHER WITH UNCERTAINTY BANDS FOR $\Delta x^2=1$ and                    |

|--------------------------------------------------------------------------------------------------------------------|

| $\Delta x^2/x^2=2\%$ . Also shown is a model prediction from the chiral quark soliton model 38                     |

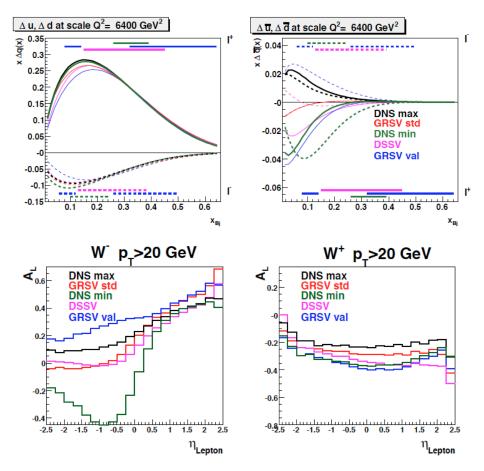

| FIGURE 23: QUARK AND ANTI-QUARK DISTRIBUTIONS FOR DIFFERENT GLOBAL FIT RESULTS (TOP) TOGETHER                      |

| WITH LEPTONIC ASYMMETRIES AS FUNCTION OF THE LEPTON RAPIDITY FOR -2.5 $\leq$ H <sub>E</sub> $\leq$ 2.5 (BOTTOM).40 |

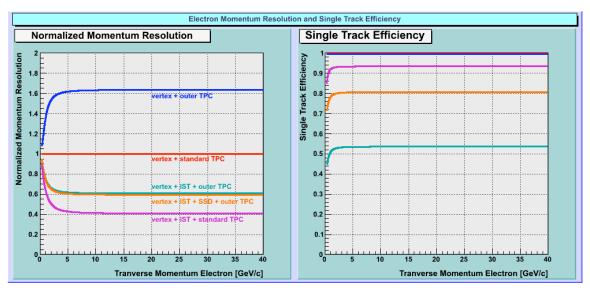

| FIGURE 24: NORMALIZED MOMENTUM RESOLUTION (LEFT) AND SINGLE TRACK EFFICIENCY (RIGHT) AS A                          |

| FUNCTION OF THE ELECTRON TRANSVERSE MOMENTUM FOR DIFFERENT TRACKING CONFIGURATIONS:                                |

| VERTEX AND STANDARD TPC (OUTER AND INNER SECTORS) (RED), VERTEX AND ONLY OUTER TPC                                 |

|                                                                                                                    |

| SECTORS (BLUE), VERTEX, IST AND ONLY OUTER TPC SECTORS (CYAN), VERTEX, IST, SSD AND ONLY                           |

| OUTER TPC SECTORS (GREEN) AND VERTEX, IST AND STANDARD TPC (YELLOW)                                                |

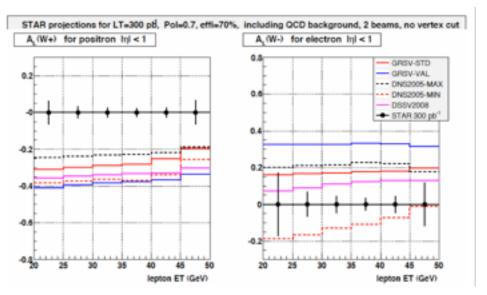

| FIGURE 25: PROJECTED UNCERTAINTIES FOR 300PB-1 AND 70% BEAM POLARIZATION OF AL AS A FUNCTION                       |

| OF ET IN THE MID-RAPIDITY ACCEPTANCE REGION OF THE STAR BEMC (-1 < H < 1)                                          |

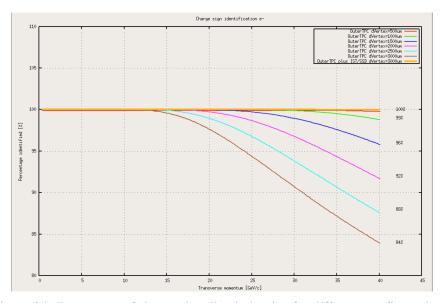

| FIGURE 26: PERCENTAGE OF CHARGE SIGN DISCRIMINATION FOR DIFFERENT CONFIGURATIONS                                   |

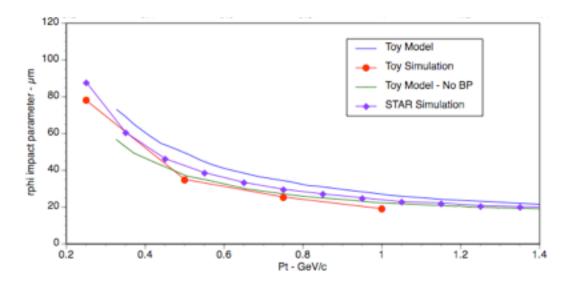

| FIGURE 27: COMPARISON OF THREE DIFFERENT TYPES OF SIMULATIONS TO DETERMINE THE POINTING                            |

| RESOLUTION IN THE $R\text{-}\phi$ direction at the vertex for kaons. The three methods are a Toy                   |

| MODEL, FAST SIMULATION, AND THE FULL STAR SIMULATION. EACH METHOD HAS DIFFERENT                                    |

| ASSUMPTIONS AND SLIGHTLY DIFFERENT PARAMETERS BUT OVERALL, THE AGREEMENT IS GOOD. IN                               |

| THE FIGURE'S LEGEND, BP IS SHORT HAND FOR "BEAM PIPE". FROM REFERENCE [4]44                                        |

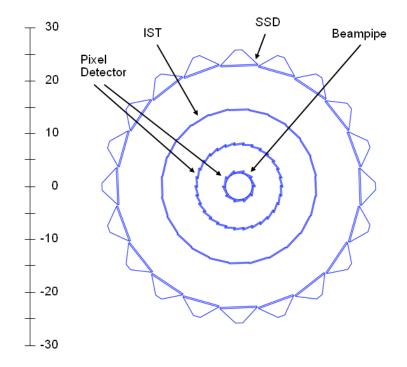

| FIGURE 28: A SCHEMATIC VIEW OF THE SI DETECTORS THAT SURROUND THE BEAM PIPE. THE SSD IS AN                         |

| EXISTING DETECTOR AND IT IS THE OUTMOST DETECTOR SHOWN IN THE DIAGRAM. THE IST LIES INSIDE                         |

| THE SSD AND THE PXL LIES CLOSEST TO THE BEAM PIPE                                                                  |

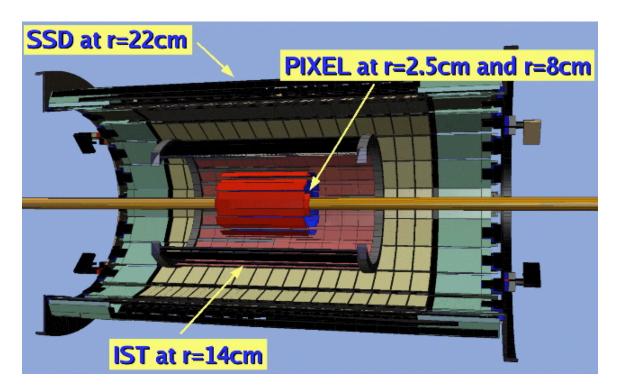

| FIGURE 29: SCHEMATIC VIEW OF THE DIFFERENT LAYERS OF THE HFT                                                       |

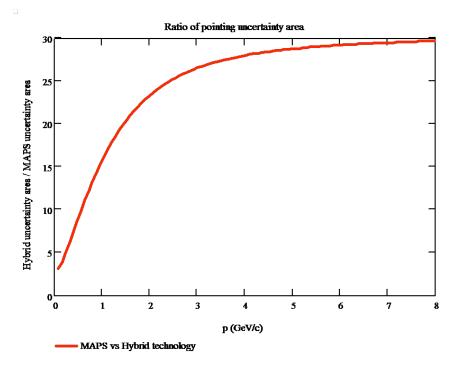

| FIGURE 30: COMPARISON OF POINTING ACCURACY OF MAPS AND HYBRID TECHNOLOGY. THE RATIO OF THE                         |

| POINTING AREA UNCERTAINY OF HYBRIDS DIVIDED BY MAPS UNCERTAINTY IS SHOWN AS A FUNCTION                             |

| OF THE MOMENTUM. AT THE LOW MOMENTUM END THE MAPS HAVE A 3 TO 1 ADVANTAGE. AT HIGH                                 |

| MOMEMTUM THE ADVANTAGE INCREASES TO 30                                                                             |

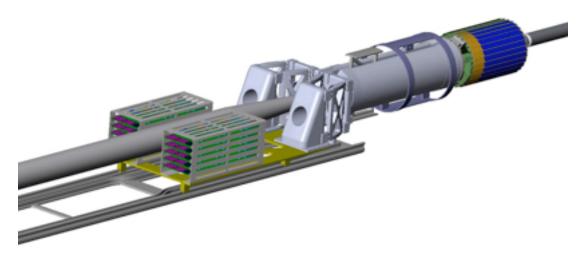

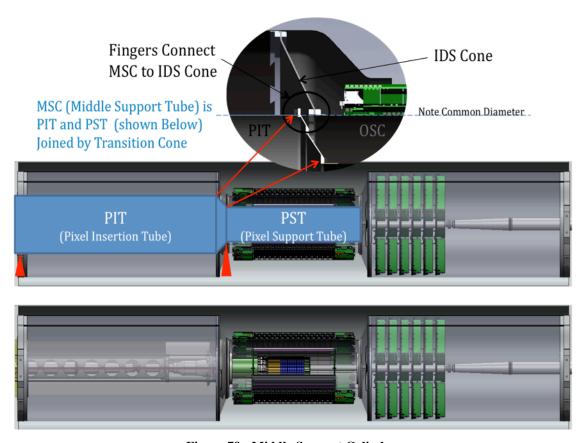

| FIGURE 31: OVERVIEW OF THE PXL DETECTOR MECHANICS SHOWING DETECTOR BARREL, SUPPORT                                 |

| STRUCTURES AND INSERTION PARTS PLUS INTERFACE ELECTRONICS BOARDS. 54                                               |

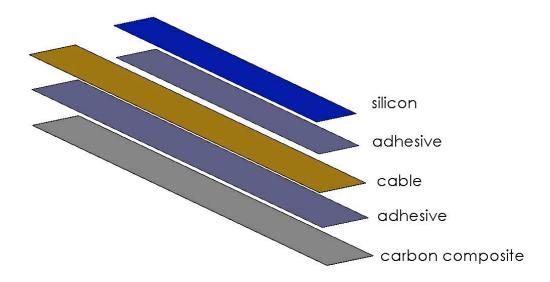

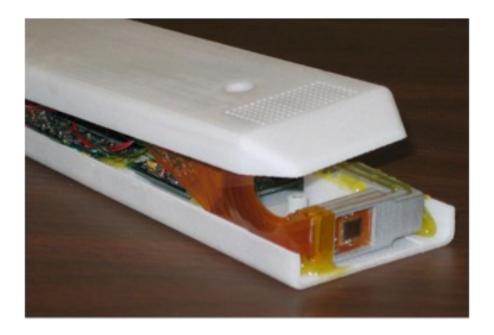

| FIGURE 32: EXPLODED VIEW OF THE LADDER SHOWING COMPONENTS. THE SILICON IS COMPOSED OF 10                           |

| SQUARE CHIPS. IT IS SHOWN HERE AS A CONTINUOUS PIECE OF SILICON, THE WAY IT HAS BEEN                               |

| MODELED FOR ANALYSIS                                                                                               |

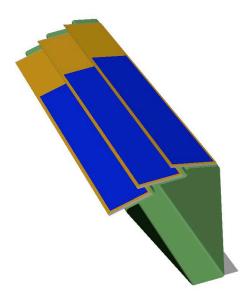

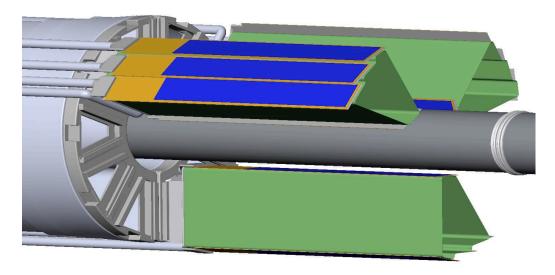

| FIGURE 33: THIN WALL CARBON SUPPORT BEAM (GREEN) CARRYING A SINGLE INNER BARREL LADDER AND                         |

| THREE OUTER BARREL LADDERS. THE BEAM IN ADDITION TO SUPPORTING THE LADDERS PROVIDES A                              |

| DUCT FOR CONDUCTING COOLING AIR AND ADDED SURFACE AREA TO IMPROVE HEAT TRANSFER TO THE                             |

| COOLING AIR                                                                                                        |

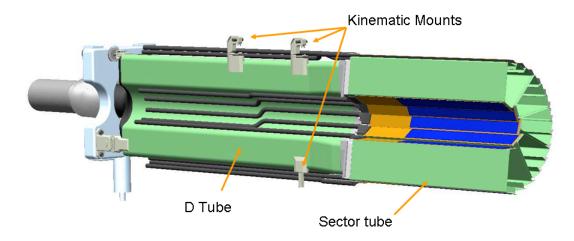

| FIGURE 34: HALF MODULE CONSISTING OF 5 SECTOR BEAM MODULES. THE SECTOR BEAM MODULES ARE                            |

| SECURED TO A CARBON COMPOSITE D TUBE USING A DOVETAIL STRUCTURE, WHICH PERMITS EASY                                |

| REPLACEMENT OF SECTOR MODULES. CARBON COMPOSITE PARTS ARE SHOWN IN GREEN FOR GREATER                               |

| VISIBILITY                                                                                                         |

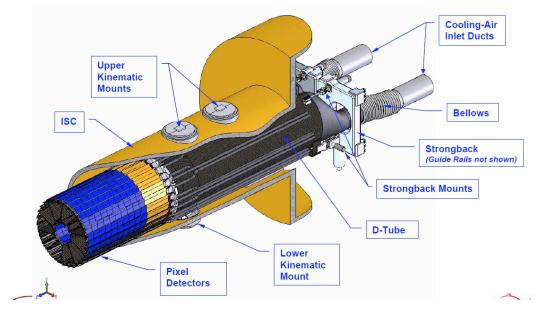

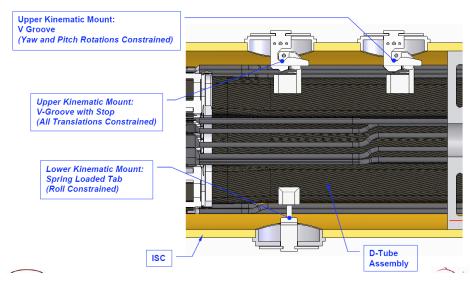

| FIGURE 35: DETECTOR ASSEMBLY IN THE INSTALLED POSITION SUPPORTED WITH THREE KINEMATIC                              |

| MOUNTS                                                                                                             |

| FIGURE 36: DETAILED VIEW OF THE KINEMATIC DOCKING MOUNTS FOR THE PXL DETECTOR. THE MOUNTS                          |

| PROVIDE A FULLY CONSTRAINED SUPPORT AND OPERATE WITH A SPRING LOADED OVER CENTER LOCK                              |

| DOWN                                                                                                               |

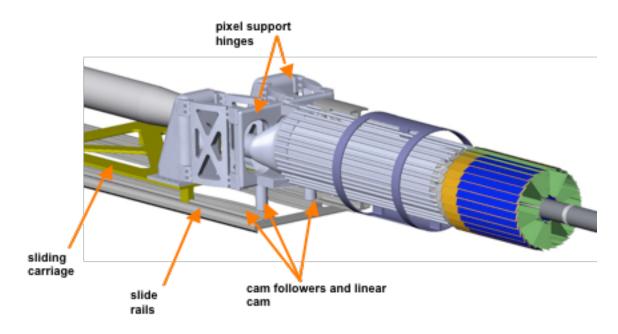

| FIGURE 37: TRACK AND CAM GUIDE SYSTEM FOR INSERTING THE DETECTOR. 58                                               |

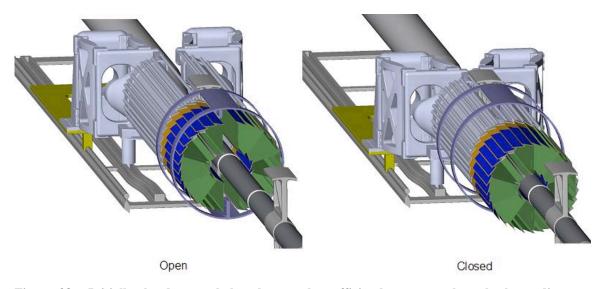

| FIGURE 38: INITIALLY THE DETECTOR HALVES HAVE TO BE SUFFICIENTLY OPEN TO CLEAR THE LARGE                           |

|                                                                                                                    |

| DIAMETER PORTION OF THE BEAM PIPE. IT THEN CLOSES DOWN SUFFICIENTLY TO FIT INSIDE THE INNER                        |

| FIELD CAGE (IFC) WHILE CLEARING THE BEAM PIPE SUPPORTS AND THEN FINALLY IT CLOSES DOWN TO                          |

| THE FINAL POSITION WITH COMPLETE OVERLAPPING COVERAGE OF THE BARRELS                                               |

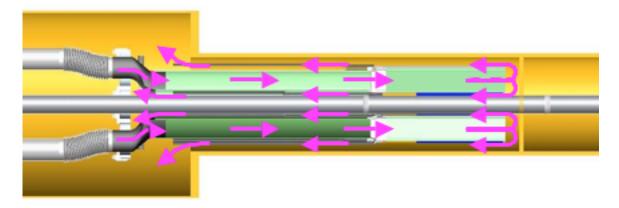

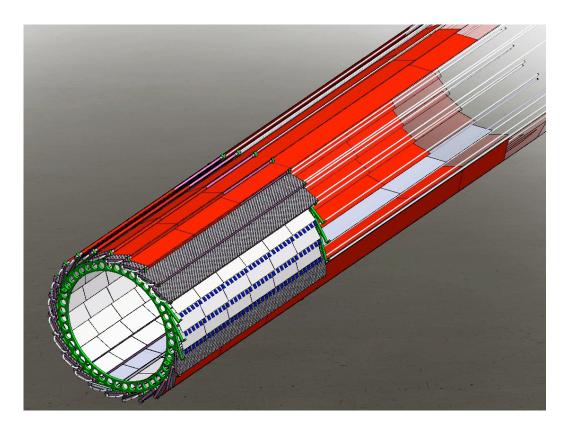

| FIGURE 39: PXL DETECTOR COOLING AIR PATH. THE AIR FLOWS DOWN THE CENTER OF THE SECTOR                              |

| MODULES AND RETURNS BACK OVER THE DETECTOR LADDERS ON THE SECTOR MODULES AND INTO THE                              |

| LARGER ISC VOLUME WHERE IT IS DUCTED BACK TO THE AIR COOLING UNIT                                                  |

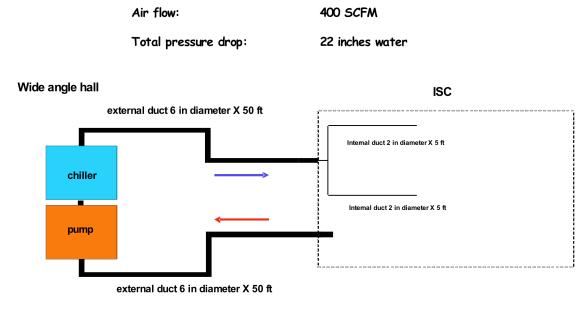

| FIGURE 40: SCHEMATIC OUTLINE OF AIR COOLING SYSTEM FOR THE PXL DETECTOR                                            |

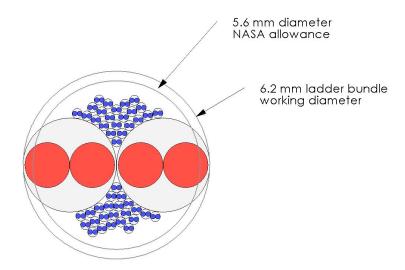

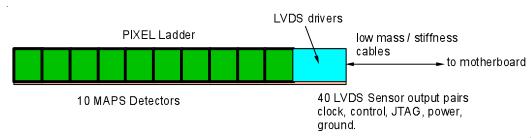

| FIGURE 41: CABLE BUNDLE ENVELOPE FOR THE LADDER CONNECTIONS. THE BLUE PAIRS INCLUDE 40                             |

| SIGNAL PAIRS, CLOCK AND TRIGGER LINES AND JTAG COMMUNICATION. THE RED CONDUCTORS ARE                               |

| FOR POWER 60                                                                                                       |

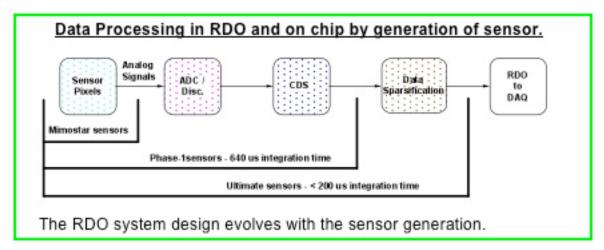

| FIGURE 42: DIAGRAM SHOWING THE SENSOR DEVELOPMENT PATH OF SENSORS FOR THE STAR PXL           |            |

|----------------------------------------------------------------------------------------------|------------|

| DETECTOR AT IPHC IN STRASBOURG. THE READOUT DATA PROCESSING REQUIRED IS SHOWN AS A           |            |

| FUNCTION OF SENSOR GENERATION.                                                               | 62         |

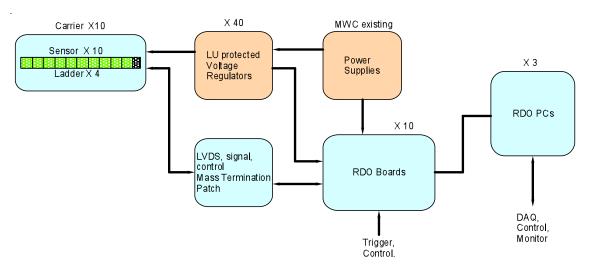

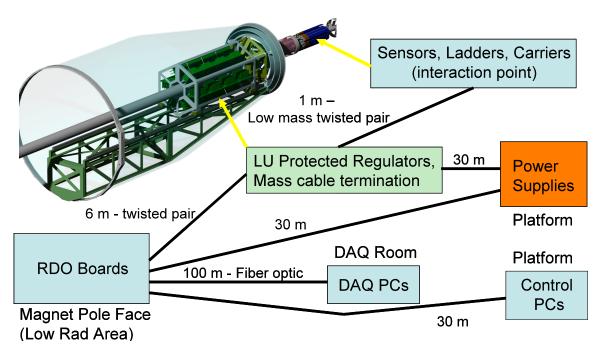

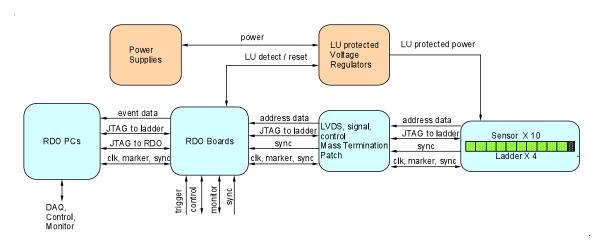

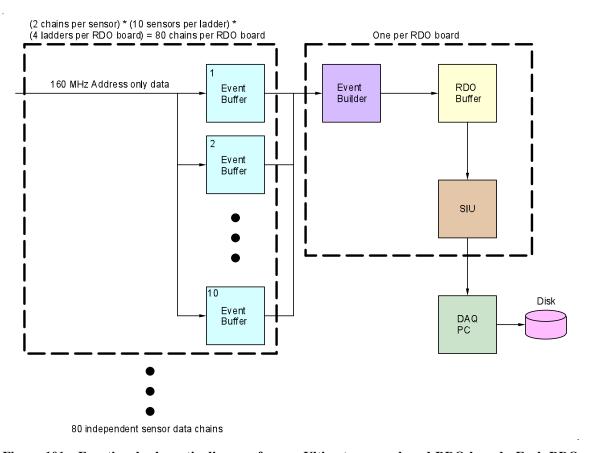

| FIGURE 43: FUNCTIONAL BLOCK SCHEMATIC FOR THE READOUT FOR THE PHASE-1 PROTOTYPE SYSTEM. TH   |            |

| DETECTOR LADDERS AND ACCOMPANYING READOUT SYSTEM HAVE A HIGHLY PARALLEL                      |            |

| ARCHITECTURE. ONE SYSTEM UNIT OF SENSOR ARRAY / READOUT CHAIN IS SHOWN. THERE ARE TEN        |            |

| PARALLEL SENSOR ARRAY / READOUT CHAIN UNITS IN THE FULL SYSTEM.                              | 64         |

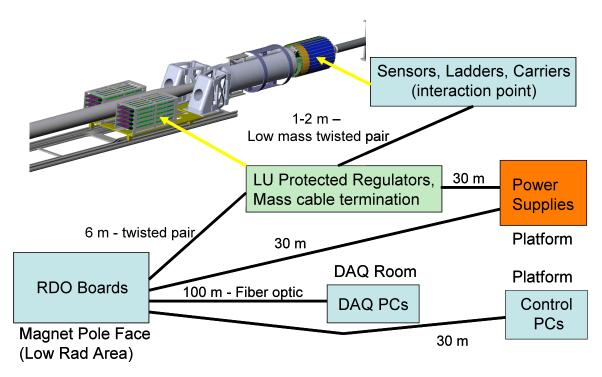

| FIGURE 44: PHYSICAL LAYOUT OF THE READOUT SYSTEM BLOCKS. THIS LAYOUT WILL BE THE SAME FOR    |            |

| BOTH THE PHASE-1 BASED PATCH AND THE FINAL PXL DETECTOR SYSTEM                               | 64         |

| FIGURE 45: ASSEMBLY OF SENSORS ON A LOW RADIATION LENGTH KAPTON FLEX CABLE WITH ALUMINUM     |            |

| CONDUCTORS. THE SENSORS ARE CONNECTED TO THE CABLE WITH BOND WIRES ALONG ONE EDGE OF         | ,          |

| THE LADDER                                                                                   |            |

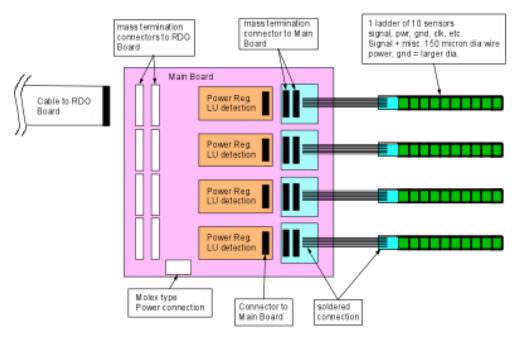

| FIGURE 46: POWER AND MASS-TERMINATION BOARD BLOCK DIAGRAM. THE DIGITAL SIGNALS TO AND FROM   |            |

| THE SENSORS ARE ROUTED THROUGH THE MAIN BOARD AND ARE CONNECTED TO THE READOUT               |            |

| BOARDS VIA THE MASS TERMINATION CONNECTORS ON THE MAIN BOARD. LATCH-UP PROTECTED             |            |

| POWER REGULATION IS PROVIDED TO EACH LADDER BY A DAUGHTER CARD MOUNTED TO THE MAIN           |            |

| BOARD. THE MAIN POWER SUPPLIES WILL BE LOCATED FAR FROM THE DETECTOR (IN THE STAR            |            |

| RACKS)                                                                                       | 66         |

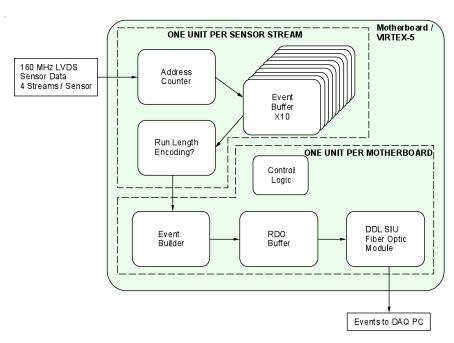

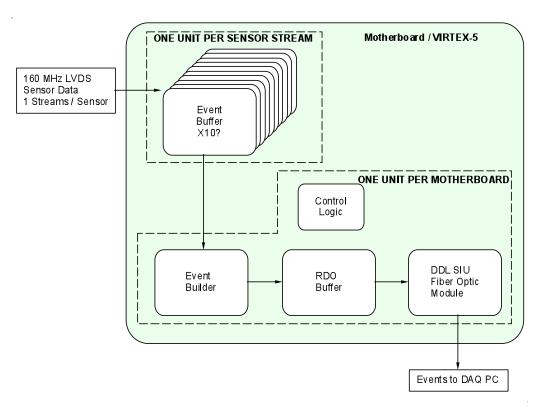

| FIGURE 47: READOUT BOARD. THE READOUT SYSTEM CONSISTS OF TWO BOARDS PER SECTOR OF 40         | 00         |

| SENSORS. A COMMERCIAL XILINX VIRTEX-5 DEVELOPMENT BOARD IS MATED TO A CUSTOM                 |            |

| MOTHERBOARD THAT PROVIDES ALL OF THE I/O FUNCTIONS INCLUDING RECEIVING AND BUFFERING         |            |

| THE SENSOR DATA OUTPUTS, RECEIVING THE TRIGGER FROM STAR, AND SENDING THE BUILT EVENTS       |            |

| TO A STAR DAQ RECEIVER PC VIA A FIBER OPTIC CONNECTION.                                      |            |

| FIGURE 48: FUNCTIONAL BLOCK DIAGRAM OF THE DATA FLOW ON THE RDO BOARDS.                      |            |

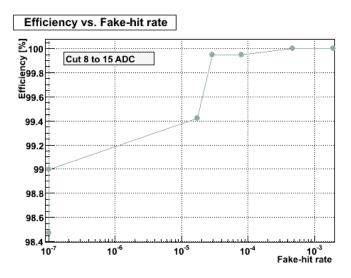

| FIGURE 49: EFFICIENCY VERSUS FAKE HIT RATE FOR A SIMPLE THRESHOLD CUT ON SIGNAL LEVEL. THE   | 51         |

| FIGURE IS OBTAINED FROM LIVE-BEAM DATA TAKEN WITH THE MIMOSTAR-2 SENSORS                     | 67         |

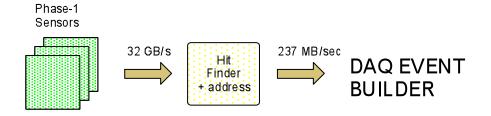

| FIGURE 50: SYSTEM LEVEL FUNCTIONALITY DIAGRAM OF THE READOUT OF THE PXL SENSORS. ONE OF THE  |            |

| TEN PARALLEL READOUT CHAINS IS SHOWN.                                                        |            |

| FIGURE 51: DATA RATE REDUCTION IN THE PHASE-1 READOUT SYSTEM.                                |            |

| FIGURE 52: FUNCTIONAL BLOCK DIAGRAM OF THE RDO BOARDS FOR THE READOUT OF THE ULTIMATE        | , 0        |

| DETECTOR BASED PXL DETECTOR.                                                                 | 71         |

| FIGURE 53: THREE MIMOSTAR-2 SENSORS IN THE TELESCOPE CONFIGURATION USED IN THE BEAM TEST AT  |            |

| STAR                                                                                         | 72         |

| FIGURE 54: PROPOSED PXL CONFIGURATION FOR THE ENGINEERING PROTOTYPE.                         | 73         |

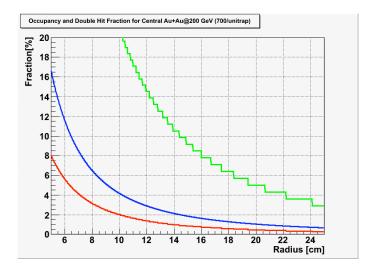

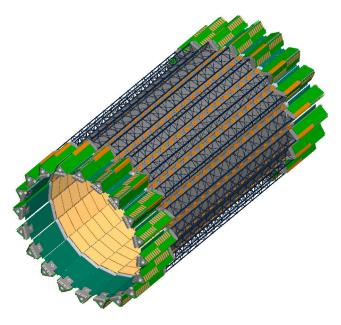

| FIGURE 55: SOLIDWORKS MODEL OF THE IST.                                                      |            |

| FIGURE 56: OCCUPANCY [BLUE CURVE] AND DOUBLE-HIT FRACTION FOR A SILICON STRIP DETECTOR [GREE |            |

| CURVE] AND A SILICON PAD SENSOR [RED CURVE]                                                  | 76         |

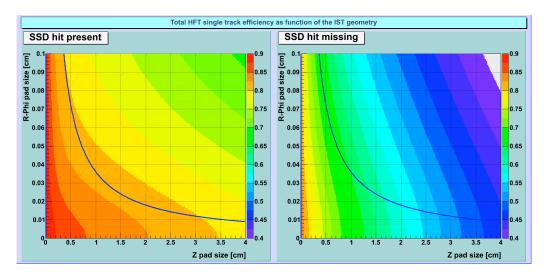

| FIGURE 57: SINGLE TRACK FINDING EFFICIENCY FOR DIFFERENT R-φ AND Z PAD SIZES OF THE IST. THE |            |

| SOLID LINE SHOWS AN ISO-LINE FOR 768 READOUT CHANNELS. THE LEFT PANEL SHOWS THE              |            |

| EFFICIENCY WHEN HITS FROM THE SSD ARE INCLUDED. IN THE RIGHT PANEL THE SSD HITS ARE NOT      |            |

| INCLUDED IN THE TRACK. PARTICLES TRACKED ARE KAONS AT 750 MeV/c                              |            |

| FIGURE 58: SINGLE-TRACK EFFICIENCY AS A FUNCTION OF THE IST BARREL RADIUS. THE ASSUMED       |            |

| Internal sensor geometry was 600 $\mu m$ in $R$ - $\phi$ and 6000 $\mu m$ in $Z$             | 77         |

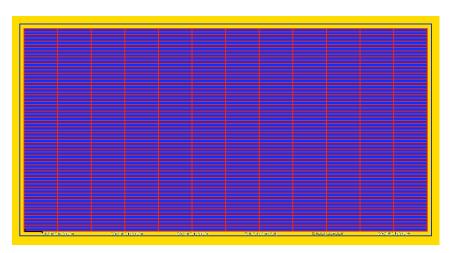

| FIGURE 59: THE SILICON PAD SENSOR INTERNAL LAYOUT.                                           |            |

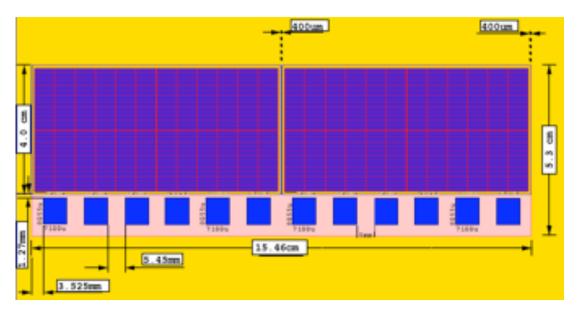

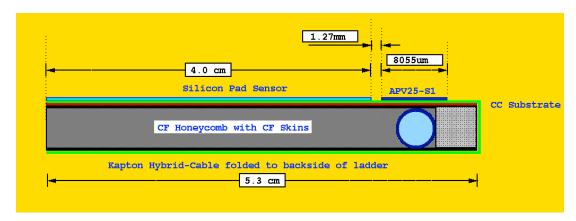

| FIGURE 60: LAYOUT OF AN IST MODULE.                                                          |            |

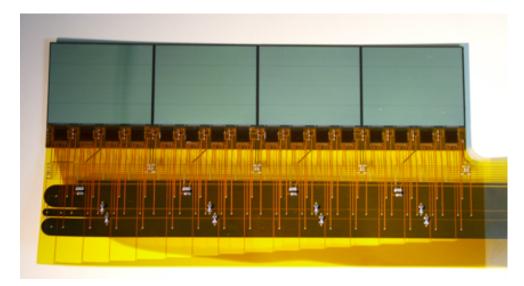

| FIGURE 61: IST PROTOTYPE WITH 4 PHOBOS IV SENSORS AND 16 APV25-S1 READOUT CHIPS.             |            |

| FIGURE 62: LONG IST PROTOTYPE LADDER MADE OUT OF CARBON FIBER HONEYCOMB AND CARBON FIBER     |            |

| SKINS. THIS PROTOTYPE HAS ONE COOLING CHANNEL.                                               |            |

| FIGURE 63: CROSS-SECTION OF THE LADDER AND MODULES. THE KAPTON HYBRID SHOWN IN GREEN IS      | <i>J</i> 1 |

| FOLDED OVER TO THE BACK SIDE.                                                                | 82         |

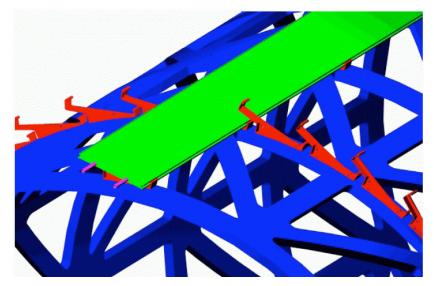

| FIGURE 64: LADDER 'CLIP' MOUNTING OF THE IST LADDERS ONTO THE SUPPORTING CYLINDER (ISC)      | -          |

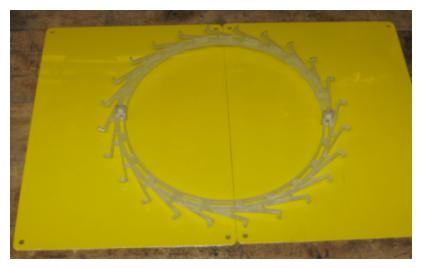

| FIGURE 65: RAPID PROTOTYPE OF THE IST LADDER MOUNTING STRUCTURE.                             |            |

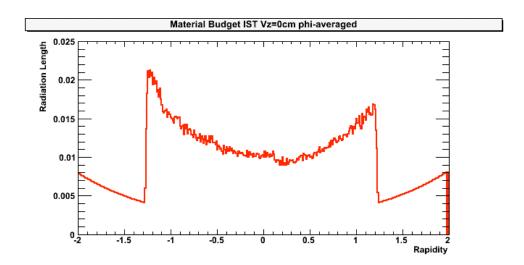

| FIGURE 66: PHI AVERAGED MATERIAL BUDGET FOR THE IST EADDER MOONTING STRUCTION OF RAPIDITY.   |            |

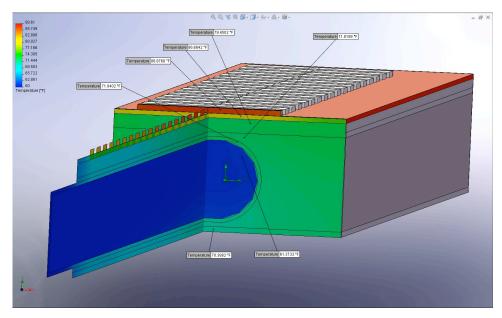

| FIGURE 67: FLOWORKS SIMULATION OF A LIQUID COOLED IST LADDER.                                |            |

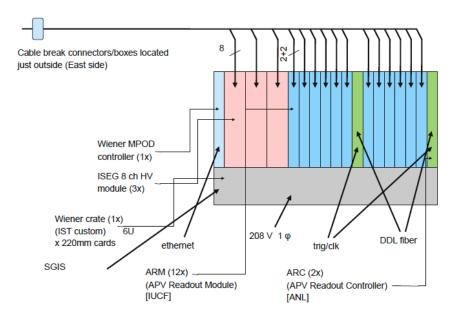

| FIGURE 68: IST DAQ BLOCK DIAGRAM                                                             |            |

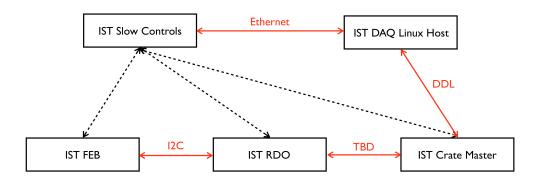

| FIGURE 69: IST SLOW CONTROLS FLOW DIAGRAM.                                                   |            |

|                                                                                              |            |

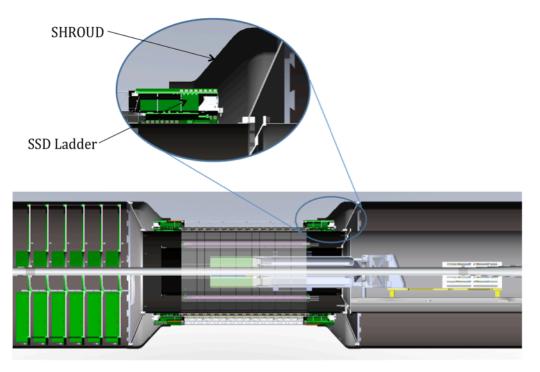

| FIGURE 70: A CAD MODEL OF THE SSD. THE RECTANGULAR GOLD OBJECTS IN THE INSIDE OF THE          |     |

|-----------------------------------------------------------------------------------------------|-----|

| CYLINDER REPRESENT THE SILICON. THE TRIANGULAR STRUCTURE IN THE CENTER IS THE LADDER          |     |

| SUPPORT. THE GREEN OBJECTS AT THE END REPRESENT THE READOUT ELECTRONICS (LADDER               |     |

| Board)                                                                                        | 88  |

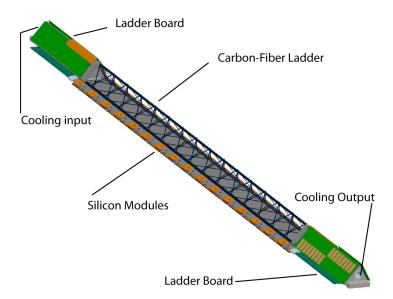

| FIGURE 71: AN SSD LADDER SHOWING ITS VARIOUS COMPONENTS. THE LADDER BOARD CONTAINS THE        |     |

| ELECTRONICS THAT READS OUT THE SILICON MODULES.                                               |     |

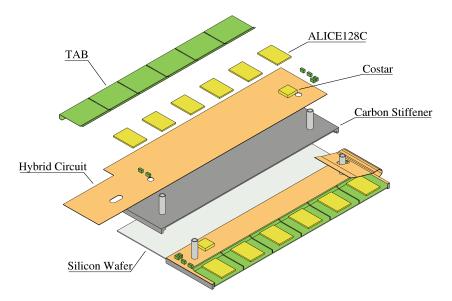

| FIGURE 72: EXPLODED VIEW OF ONE DETECTOR MODULE.                                              |     |

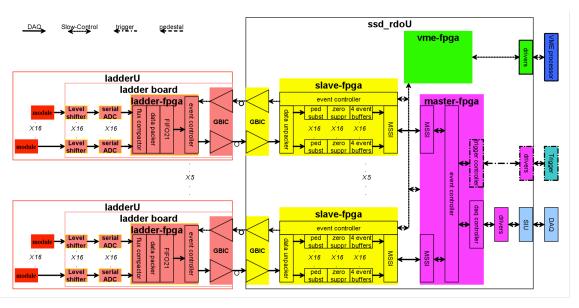

| FIGURE 73: A SCHEMATIC OF THE INTERCONNECTION BETWEEN THE LADDER ELECTRONICS AND THE RDO      |     |

| CARD, EACH RDO HANDLES 5 LADDERS. THE CONNECTION BETWEEN THE LADDER ELECTRONICS A             |     |

| THE CORRESPONDING RDO CARD IS A DUAL OPTICAL FIBER.                                           |     |

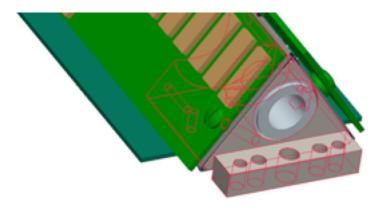

| FIGURE 74: END BRACKET FOR THE SSD THAT MOUNTS TO THE OSC. THE HOLES ARE USED FOR ALIGNM      |     |

|                                                                                               |     |

| AND TO FIX THE DETECTOR                                                                       |     |

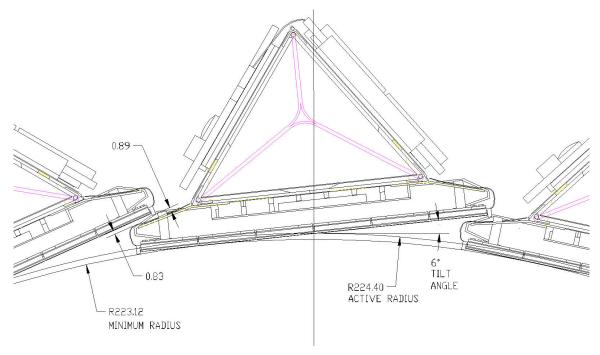

|                                                                                               | HAS |

| RECENTLY BEEN INCREASED TO 7° TO PROVIDE CLEARANCE FOR A POST ON THE MODULES. THIS            | 0.2 |

| RESULTS IN A SLIGHTLY SMALLER RADIUS.                                                         |     |

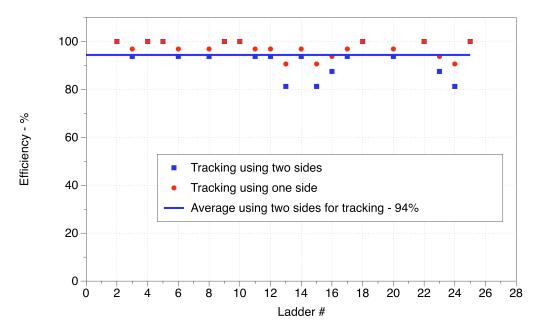

| FIGURE 76: A PLOT OF THE EFFICIENCY FOR THE EXISTING 21 LADDERS. THE BLUE POINTS ASSUME THAT  |     |

| BOTH THE N AND P SIDE ARE NEEDED IN TRACKING. THE RED POINTS ARE FOR THE CASE WHEN EITH       |     |

| SIDE IS USED.                                                                                 |     |

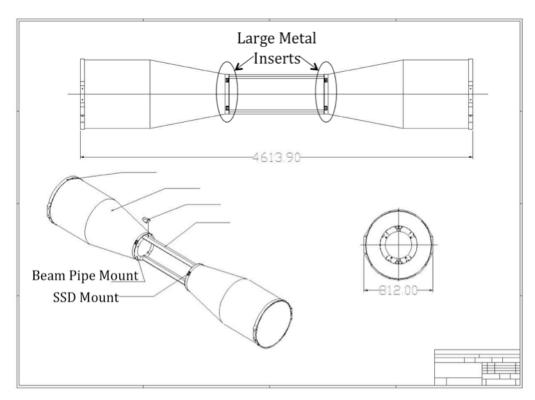

| FIGURE 77: OLD DETECTOR AND BEAM PIPE SUPPORT.                                                |     |

| Figure 78: E-field shroud.                                                                    |     |

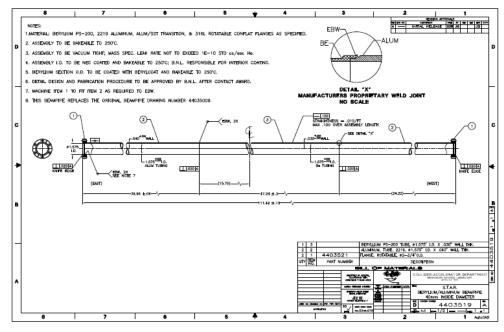

| FIGURE 79: MIDDLE SUPPORT CYLINDER                                                            |     |

| FIGURE 80: SMALL DIAMETER BEAM PIPE WITH BE MID-SECTION.                                      | 111 |

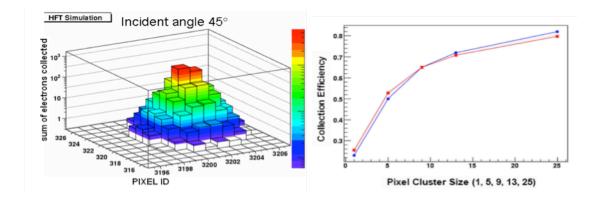

| FIGURE 81: LEFT: DISTRIBUTION OF THE NUMBER OF DEPOSITED ELECTRONS ON PIXELS FROM A CHARGEI   | D   |

| PION WITH 45 DEGREES INCIDENT ANGLE FROM THE SLOW SIMULATOR. RIGHT: PROFILE OF THE            |     |

| FRACTION OF DEPOSITED NUMBER OF ELECTRONS FROM SIMULATION (BLUE) AND DATA [54] (RED).         | 118 |

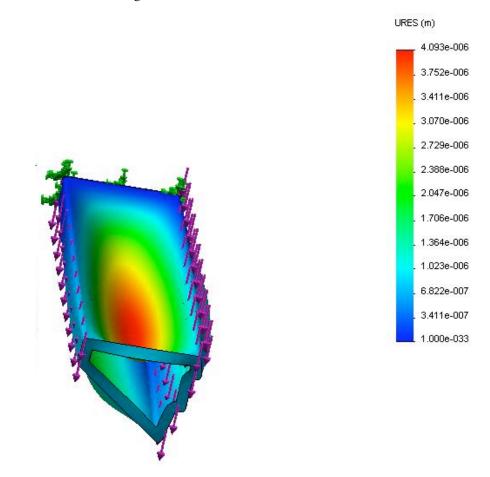

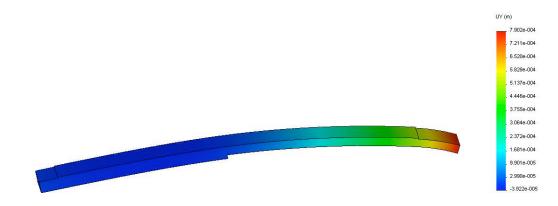

| FIGURE 82: FEA RESULTS FOR GRAVITY DEFORMATION OF A 120 MICRON CARBON COMPOSITE SUPPORT       |     |

| STRUCTURE CARRYING 4 DETECTOR LADDERS.                                                        | 135 |

| FIGURE 83: SHORT SECTION OF LADDER STRUCTURE SHOWING PROBLEMS WITH EXCESSIVE THERMAL          |     |

| BIMETAL EFFECT BENDING WITH USING STIFF ADHESIVE. THE 500 MICRON DISPLACEMENT RESULTI         | NG  |

| FROM A 20 DEG C TEMPERATURE CHANGE IS DRIVEN BY THE LARGE CTE OF THE KAPTON CABLE             | 136 |

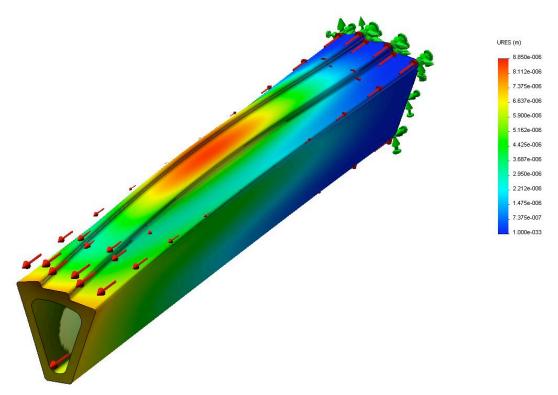

| FIGURE 84: THERMALLY INDUCED DISPLACEMENT OF A SECTOR BEAM WITH END REINFORCEMENT. THE        |     |

| MAXIMUM RESULTING DISPLACEMENT IS $9\mu\text{M}$ . The beam and end reinforcement is composed | OF  |

| 200 μm Carbon Composite                                                                       |     |

| ·                                                                                             | 137 |

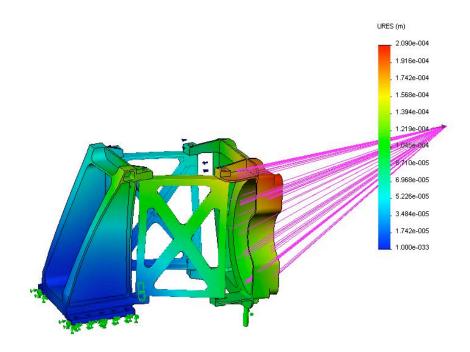

| FIGURE 85: DISPLACEMENT OF AN EARLY INSERTION HINGE DESIGN UNDER COCKING LOAD OF THE          |     |

| LATCHING MECHANISM. THE DISPLACEMENT IN THE IMAGE IS MAGNIFIED BY 140 AND THE MAXIMU          |     |

| DISPLACEMENT IS 210 MICRONS. THE PINK LINES SHOW THE POSITION OF THE REMOTE LOAD AS IT IS     |     |

| CARRIED THROUGH THE D TUBE, NOT SHOWN                                                         |     |

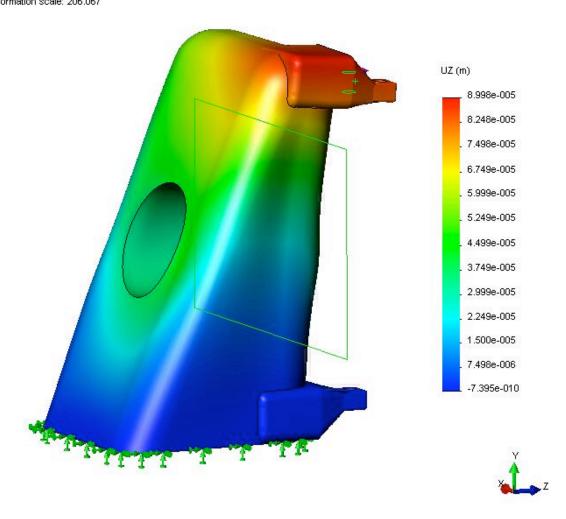

| FIGURE 86: DISTORTION OF THE SUPPORT HINGE BACKER UNDER LATCH COCKING LOAD. THE FLEXING IN    |     |

| THE BEAM AXIS DIRECTION IS 90 MICRONS.                                                        |     |

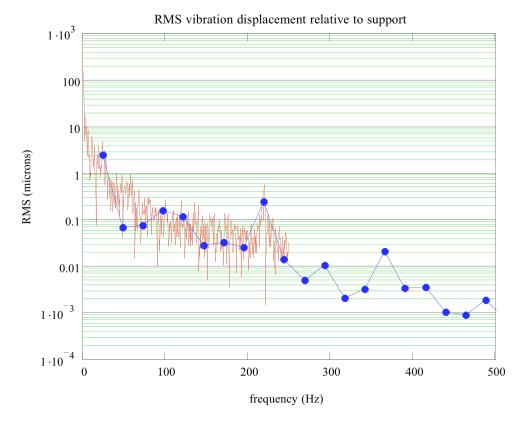

| FIGURE 87: VIBRATION RESPONSE OF A MECHANICAL HARMONIC OSCILLATOR MOUNTED ON THE TPC EN       |     |

| CAP AS DETERMINED WITH MEASUREMENTS OF AN ACCELEROMETER BOLTED TO THE TPC END CAP.            |     |

| THE TWO CURVES REPRESENT MEASUREMENTS MADE USING TWO DIFFERENT METHODS OF RECORDI             |     |

| THE DATA.                                                                                     | 140 |

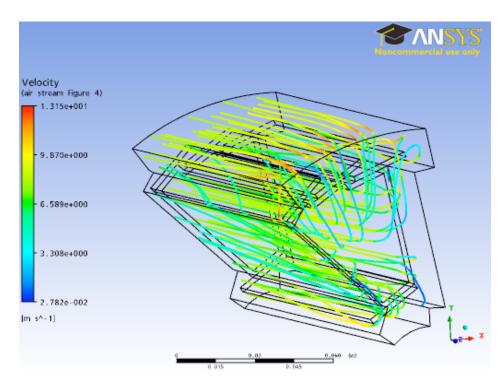

| FIGURE 88: STREAM LINES SHOWING THE COOLING AIR FLOW. THE FLOW DIRECTION IS FROM INSIDE TO    |     |

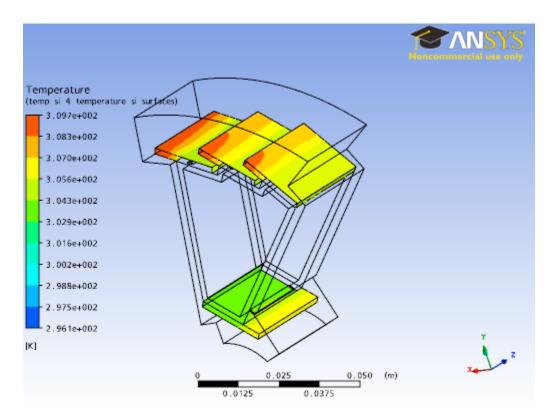

| OUTSIDE. THE COLOR CODE SHOWS AIR VELOCITY                                                    | 141 |

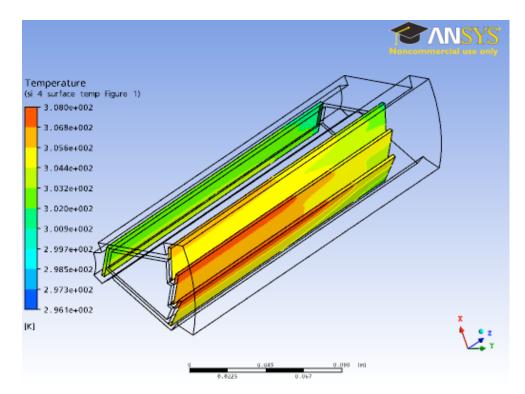

| FIGURE 89: SURFACE TEMPERATURE OF SILICON LADDERS. THE MAXIMUM TEMPERATURE INCREASE ABO       | OVE |

| AMBIENT IS 12 DEG C. THE COOLING AIR FLOWS ACROSS BOTH THE INNER AND OUTER SURFACES.          | ГНЕ |

| AIR ENTERS FROM THE LEFT ON THE INSIDE OF THE SUPPORT BEAM, TURNS AROUND AT THE RIGHT A       | ND  |

| EXITS ON THE LEFT.                                                                            | 141 |

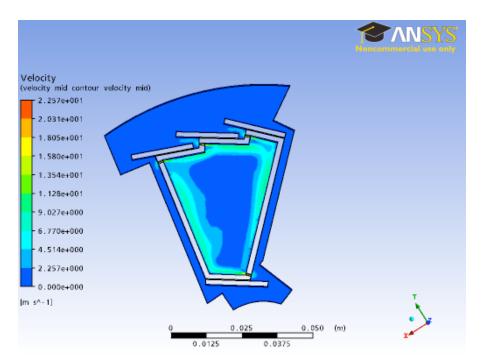

| FIGURE 90: SECTOR COOLING WITH TRANSVERSE JETS OF COOLING DIRECTED TO THE INSIDE OF THE SECT  | OR  |

| BEAM SUPPORT STRUCTURE THROUGH THIN SLOTS. THE AIR VELOCITY PROFILE IS SHOWN IN COLOR         |     |

| THE AIR VELOCITY NEAR THE SURFACES BENEATH THE LADDERS IS 11 M/S.                             |     |

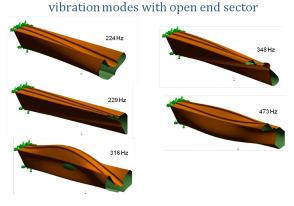

| FIGURE 91: SILICON SURFACE TEMPERATURE PROFILE FOR THE TRANSVERSE COOLING JET DESIGN          |     |

| FIGURE 92: FIRST VIBRATION MODES FOR AN OPEN ENDED SECTOR. FREQUENCIES ARE RELATIVE AS        |     |

| COMPOSITES PROPERTIES IN THE FEA ARE NOT AS-BUILT.                                            | 143 |

|                                                                                               |     |

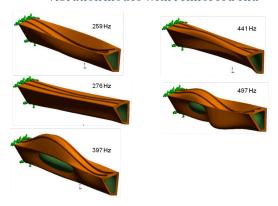

| FIGURE 93: FIRST VIBRATION MODES FOR A SECTOR WITH A REINFORCED END. FREQUENCIES ARE RELATED    |     |

|-------------------------------------------------------------------------------------------------|-----|

| AS COMPOSITE PROPERTIES IN THE FEA ARE NOT AS-BUILT.                                            |     |

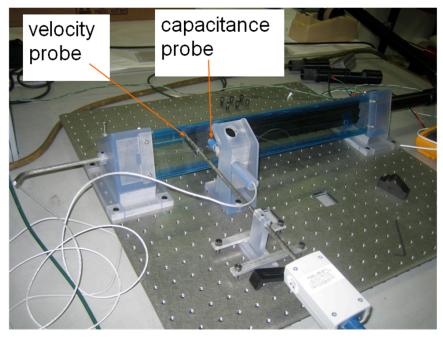

| FIGURE 94: WIND TUNNEL TO MEASURE VIBRATION OF THE SECTOR STRUCTURE INDUCED BY COOLING AI       | R   |

| FLOW. THE CARBON COMPOSITE SECTOR UNDER TEST WEIGHS 21 GM. ADDITIONAL WEIGHT WAS                |     |

| ATTACHED TO INCLUDE THE EFFECT OF INSTALLED LADDERS.                                            | 144 |

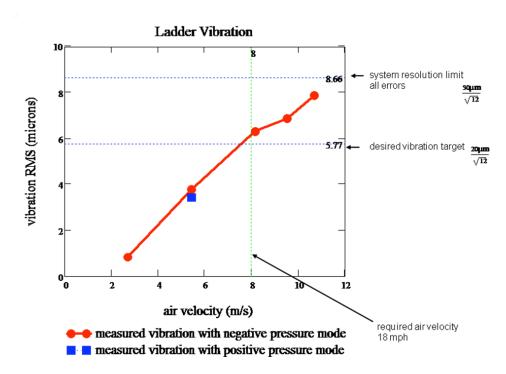

| FIGURE 95: MEASURED RMS VIBRATION OF THE MIDDLE OUTSIDE LADDER POSITION AT THE POINT OF         |     |

| MAXIMUM VIBRATION. THE SECTOR IN THIS CASE WAS OPEN ENDED, WITHOUT REINFORCEMENT                |     |

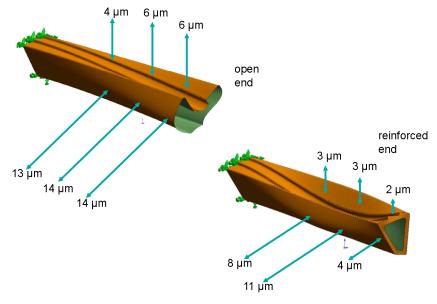

| FIGURE 96: MEASURED VIBRATION AT SEVERAL POINTS ON TWO SECTOR DESIGNS, ONE WITH AN OPEN EN      |     |

| AND ANOTHER WITH A REINFORCED END. THE FIRST VIBRATION MODES FROM FEA ARE SHOWN FOR             |     |

| QUALITATIVE COMPARISON. THE TOP POSITION MEASUREMENTS GIVE THE LADDER VIBRATION WHI             | CH  |

| is of interest because this affects the detector performance. The 3 $\mu\text{m}$ value is well |     |

| WITHIN OUR $20\mu\text{m}$ requirement. The side vibration does not affect detector positions   | 145 |

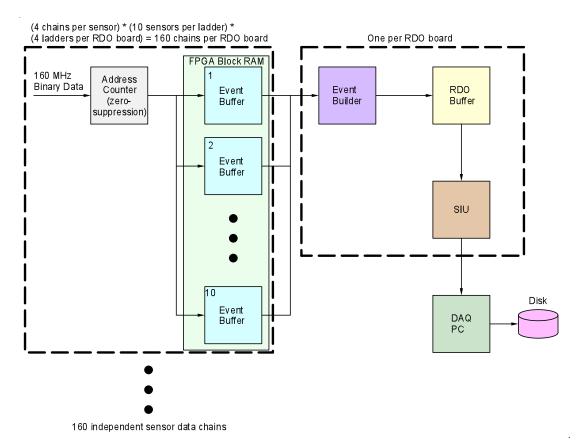

| FIGURE 97: FUNCTIONAL SCHEMATIC DIAGRAM FOR ONE PHASE-1 SENSOR BASED RDO BOARD. EACH RD         | DO  |

| BOARD SERVICES ONE INNER LADDER AND 3 OUTER LADDERS. EACH LADDER CONTAINS 10 SENSOR             | S.  |

|                                                                                                 | 147 |

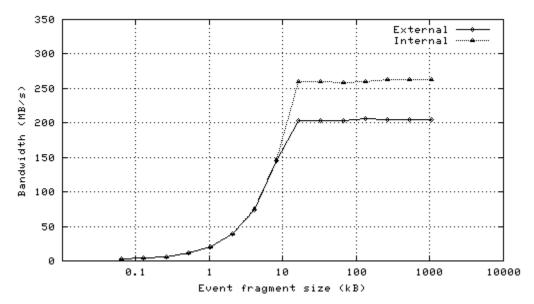

| FIGURE 98: BANDWIDTH OF A SINGLE CHANNEL OF THE SIU - RORC FIBER OPTIC LINK AS A FUNCTION OF    |     |

| EVENT FRAGMENT SIZE WITH AN INTERNAL AND EXTERNAL (DDL) DATA SOURCE USING TWO D-RO              | ORC |

| CHANNELS. FIGURE TAKEN FROM THE LECC 2004 WORKSHOP IN BOSTON.                                   |     |

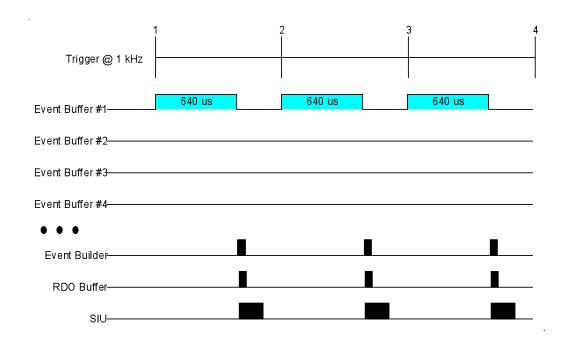

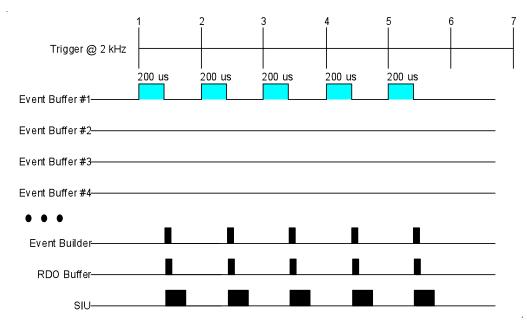

| FIGURE 99: CHRONOGRAM OF THE PHASE-1 BASED READOUT SYSTEM FUNCTIONS FOR A 1 KHZ PERIODIC        |     |

| TRIGGER.                                                                                        | 149 |

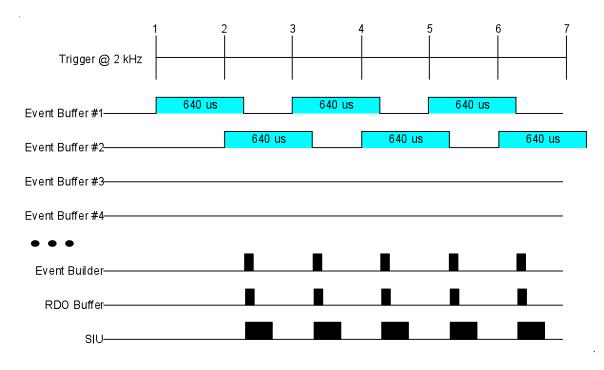

| FIGURE 100: CHRONOGRAM OF THE PHASE-1 BASED READOUT SYSTEM FUNCTIONS FOR A 2 KHZ PERIODIC       |     |

| TRIGGER.                                                                                        | 149 |

| FIGURE 101: FUNCTIONAL SCHEMATIC DIAGRAM FOR ONE ULTIMATE SENSOR BASED RDO BOARD. EACH          | Ι   |

| RDO BOARD SERVICES ONE INNER LADDER AND 3 OUTER LADDERS. EACH LADDER CONTAINS 10                |     |

| SENSORS                                                                                         | 150 |

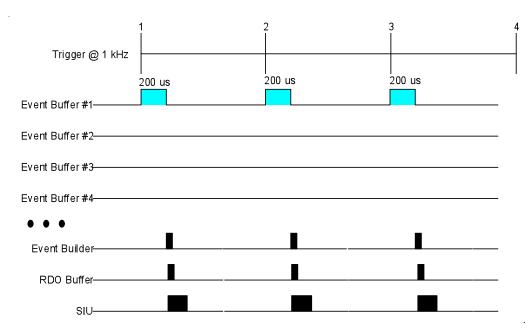

| FIGURE 102: CHRONOGRAM OF THE ULTIMATE SENSOR BASED READOUT SYSTEM FUNCTIONS FOR A 1 KH         | Z   |

| PERIODIC TRIGGER.                                                                               |     |

| FIGURE 103: CHRONOGRAM OF THE ULTIMATE SENSOR BASED READOUT SYSTEM FUNCTIONS FOR A 2 KH         | Z   |

| PERIODIC TRIGGER.                                                                               |     |

| FIGURE 104: PHYSICAL LAYOUT OF THE RDO SYSTEM.                                                  |     |

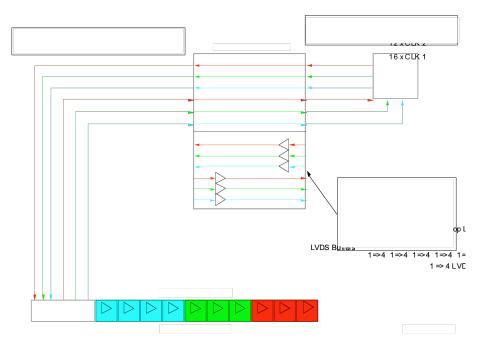

| FIGURE 105: FUNCTIONAL BLOCK DIAGRAM OF THE LVDS DATA PATH TEST SYSTEM.                         |     |

| FIGURE 106: MOCK LADDER PCB AS USED IN THE TESTS.                                               |     |

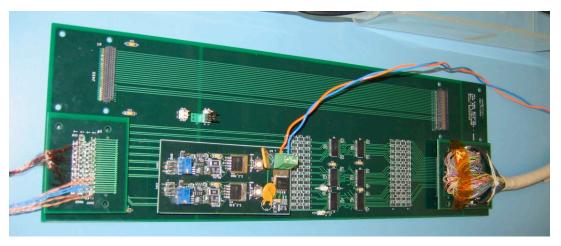

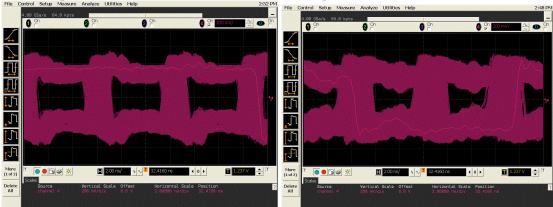

| FIGURE 107: MASS TERMINATION BOARD AS USED IN THE TEST. LADDER CONNECTIONS ARE ON THE LEFT      |     |

| HAND SIDE OF THE BOARD, A 6M CABLE TO THE VIRTEX5 INTERFACE RDO BOARD IS ON THE RIGHT.          |     |

| THE DAUGHTER CARD MOUNTED IN THE MIDDLE OF THE BOARD SUPPLIES LATCH UP PROTECTED AND            |     |

| MONITORED POWER. NOTE THAT THERE ARE TWO DATA PATHS. ONE IS UN-BUFFERED AND THE OTH             |     |

| IS BUFFERED THROUGH FIN1108 LVDS BUFFERS.                                                       |     |

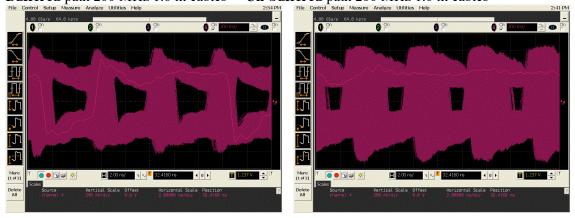

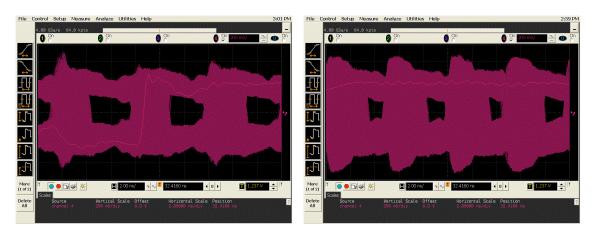

| FIGURE 108: VIRTEX-5 INTERFACE BOARD MOUNTED TO THE XILINX VIRTEX-5 DEVELOPMENT BOARD. T        | HE. |

| TOP VIEW IS SHOWN IN THE LEFT HAND DIAGRAM. IT SHOWS THE XILINX VIRTEX-5 DEVELOPMENT            |     |

| BOARD ON TOP WITH THE SIU VISIBLE ON THE V5IB. THE PHOTOGRAPH ON THE RIGHT SHOWS THE            |     |

| CABLE ATTACHMENT AND TEST POINTS ON THE V5IB.                                                   | 156 |

# **List of Tables**

| Table 1: The set of cut values used for D $^{ m v}$ reconstruction                                   | . 16 |

|------------------------------------------------------------------------------------------------------|------|

| TABLE 2: SUMMARY OF RADIATION LENGTH AND IMPACT PARAMETER RESOLUTION. THE ORIGINAL HFT               |      |

| PIXEL DESIGN IS COMPARED WITH THE CURRENT LADDER DESIGN AND THE WORST-CASE EXAMPLE                   |      |

| WHERE THE ALUMINUM IN THE LADDER CABLE IS REPLACED WITH COPPER.                                      |      |

| Table 3: Signal significance, purity and number of produced and reconstructed $\Lambda_{C}$ in 500 M |      |

| CENTRAL AU+AU COLLISIONS (FOR NO $\Lambda_{C}/D^{0}$ ENHANCEMENT). DECAY BRANCHING RATIO,            |      |

| ACCEPTANCE, EFFICIENCY AND TOPOLOGICAL CUTS ARE TAKEN INTO ACCOUNT.                                  |      |

| Table 4: Same as Table 3, for 500 M peripheral Au+Au collisions.                                     |      |

| Table 5: D and B meson parameters.                                                                   |      |

| Table 6: Ratios for two different DCA cuts                                                           |      |

| Table 7: HFT Performance requirements.                                                               |      |

| TABLE 8: POINTING RESOLUTION OF THE TPC AND HFT DETECTORS AT INTERMEDIATE POINTS ALONG THI           |      |

| PATH OF A 750 MEV KAON AS IT IS TRACKED FROM THE OUTSIDE – IN.                                       |      |

| Table 9: Performance parameters for the PXL detector.                                                |      |

| Table $10\colon$ Preliminary estimate of heat load on the chiller for the PXL air cooling system     |      |

| Table 11: Specifications of the Phase-1 and Ultimate sensors.                                        |      |

| Table 12: Parameters used to calculate data rates from a Phase-1 based system                        |      |

| Table 13: Parameters used to calculate data rates from an Ultimate sensor based system               |      |

| Table 14: Specifications for the IST.                                                                |      |

| Table 15: Summary of SSD characteristics and performances.                                           |      |

| Table 16: Estimated power consumption for a ladder                                                   |      |

| Table 17: Mean electronics temperatures measured on the test ladders with cooling off. $$ T          |      |

| AMBIENT AIR TEMPERATURE WAS 19°C.                                                                    |      |

| TABLE 18: MEAN ELECTRONICS TEMPERATURES MEASURED ON THE TEST LADDER WITH COOLING ON. THI             | Е    |

| AMBIENT AIR TEMPERATURE AND INPUT AIR TEMPERATURE WAS 19°C.                                          | . 93 |

| TABLE 19: MEAN TEMPERATURES MEASURED AT VARIOUS POINTS ALONG THE TEST LADDER WITH THE                |      |

| COOLING SYSTEM TURNED ON. THE COLUMN ON THE LEFT IDENTIFIES THE WAFER NUMBER (1-16)                  | . 94 |

| TABLE 20: SSD SERVICES PARAMETERS. THE TOTAL AREA IS CALCULATED IN SQUARE CENTIMETERS, NOT           | Γ    |

| ACCOUNTING FOR PACKING FRACTION. THE DIAMETER OF THE AIR-COOLING IS TAKEN FROM THE SIZ               | ĽΕ   |

| OF THE ORIGINAL SSD DESIGN.                                                                          | . 96 |

| Table 21: Summary of institutional responsibilities.                                                 | 120  |

| TABLE 22: HFT SUBSYSTEMS AND MANAGERS.                                                               | 125  |

| TABLE 23: HFT INTEGRATED PROJECT TEAM                                                                | 126  |

| Table 24: Participating HFT institutions.                                                            |      |

| Table 25: HFT Milestone level 0.                                                                     | 128  |

| Table 26: High level project milestones                                                              | 128  |

| Table 27: Level 2 milestones.                                                                        |      |

| TABLE 28: TOTAL PROJECT COST RANGE WITH CONTINGENCY.                                                 |      |

| TABLE 29: PROJECT COST BY FISCAL YEAR AND BY FUNDING SOURCE.                                         |      |

| Table 30: Parameters for the Phase-1 based detector system used in the example calculation           |      |

| SHOWN BELOW.                                                                                         |      |

| Table 31: Parameters for the Ultimate sensor based detector system                                   |      |

| Table 32: Bit error rates for two different configurations.                                          | 158  |

#### 1. Introduction

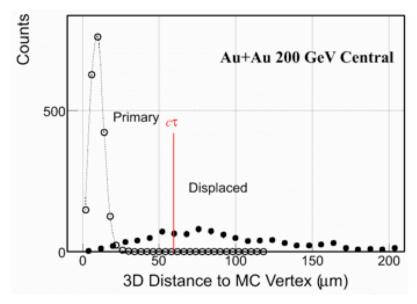

The Heavy Flavor Tracker (HFT) is a state-of-the-art micro-vertex detector utilizing active pixel sensors and silicon strip technology. The HFT will significantly extend the physics reach of the STAR experiment for precision measurements of the yields and spectra of particles containing heavy quarks. This will be accomplished through topological identification of mesons and baryons containing charm quarks, such as  $D^{\circ}$  and  $\Lambda_c$ , by the reconstruction of their displaced decay vertices with a precision of approximately 50  $\mu$ m in p+p, d+A, and A+A collisions. The combined measurements of directly identified charm hadrons and of the total non-photonic electrons will enable us to identify the bottom production at RHIC, including the bottom production cross section and  $R_{AA}$  and  $v_2$  of the decay electrons.

The HFT consists of 4 layers of silicon detectors grouped into three subsystems with different technologies, guaranteeing increasing resolution when tracking from the TPC towards the vertex of the collision. The Silicon Strip Detector (SSD) is an existing detector in double-sided strip technology. It forms the outermost layer of the HFT. The Intermediate Silicon Tracker (IST), consisting of a layer of single-sided strip-pixel detectors, is located inside the SSD. Two layers of silicon pixel detector (PXL) are inside the IST. The pixel detectors have the resolution necessary for a precision measurement of the displaced vertex. With the HFT, the Time-of-Flight detector and the TPC we will study the physics of mid-rapidity charm and bottom production.

The pixel detector will use CMOS Active Pixel Sensors (APS), an innovative technology never used before in a collider experiment. The APS sensors are only 50  $\mu$ m thick with the first layer at a distance of only 2.5 cm from the interaction point. This opens up a new realm of possibilities for physics measurements. In particular, a thin detector (0.37% of a radiation length per layer) in STAR makes it possible to do the direct topological reconstruction of open charm hadrons down to very low transverse momentum by the identification of the charged daughters of the hadronic decay.

## 2. Physics Motivation

The primary motivation for the HFT is to extend STAR's capability to study heavy flavor production by the measurement of displaced vertices and to do the direct topological identification of open charm hadrons. The yield and distribution of bottom hadrons will be estimated from charm production and non-photonic electron measurements but also via the impact parameter reconstruction of their decay electrons. Heavy quark measurements are a key component of the heavy ion program at RHIC as it moves from the discovery phase to the systematic characterization of the dense medium created in heavy ion collisions. The primary physics topics to be addressed by the HFT include heavy flavor energy loss, flow, and a test of partonic thermalization at RHIC. These measurements have been identified as necessary goals for the RHIC program in the Nuclear Physics Long Range Plan and in the RHIC mid-term scientific plan.

From a precise measurement of the spectra and the production ratios of charm hadron states, we will be able to extrapolate to the total yield for charm quark production. Furthermore, the open charm production rate is high enough at RHIC that the coalescence process becomes relevant for charmonium production. Knowledge of the total production cross-section for charm quarks is also essential as a baseline for  $J/\psi$  measurements. A meaningful answer to the question of  $J/\psi$  production at RHIC requires knowledge of the charm production cross-section in heavy ion reactions.

A unique advantage of STAR due to its full azimuthal coverage is the detailed studies of charm-charm correlations. In pQCD, heavy quarks are produced back-to-back at relatively large Q². The angular correlation will be modified in HI collisions due to the interactions between the heavy quarks and the medium. How much and how fast the changes of the heavy quark angular correlation depends on the nature of the medium. Therefore if we study the change of the D-D angular correlations we could extract the properties of the medium. Note that such study is more suitable for collisions at RHIC as the leading order dominates the production. At higher beam energies, such as LHC, the high-order contributions become more important, so the angular correlation analysis will be less obvious, more complicated. The effect of 'partonic wind' on charm quark correlations in high-energy nuclear collisions is studied in several theoretical papers¹ with D anti-D correlations as a sensitive probe for thermalization in high-energy nuclear collisions.

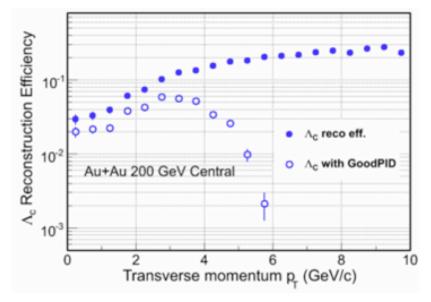

The observation of an enhancement in the ratio of baryon to meson production for particles containing light quarks was one of the interesting early observations in the RHIC program. This also was one of the supporting arguments for the quark coalescence model. With the HFT we will be able to measure the production rate for the  $\Lambda_c$  baryon. This will also allow us to study in detail the meson to baryon ratio for charm particles as a further test of the coalescence hypothesis. It will also help understand whether the  $\Lambda_c$  baryon is formed by a direct combination of a c quark with a ud di-quark (2-body process resulting in higher ratio values) or a 3-body combination.<sup>2,3</sup> The baryon to meson ratio is also important for the understanding of the flavor dependence of the energy loss mechanism.

The masses of charm and bottom quarks are about 1.25 GeV and 4.7 GeV, respectively, much higher than the predicted initial temperature of about 0.4 GeV for the matter produced in high-energy nuclear collisions at RHIC. Because are heavy, they are produced predominantly in the initial state and their intrinsic properties will not be affected by QCD interactions during the subsequent evolution. Therefore, heavy quarks can be used to probe the properties of the medium created in heavy ion collisions. The radiation of gluons is kinematically suppressed for heavy

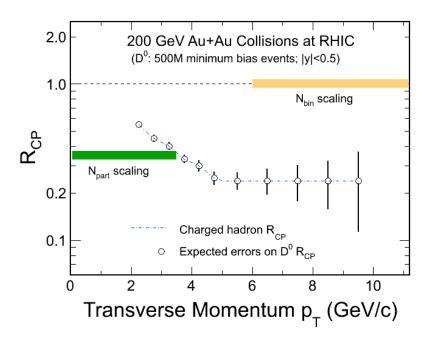

flavor quarks passing through the medium: thus they should lose less energy than the light quarks. An important measurement to be made with the HFT is  $R_{\rm CP}$ , the ratio of charm mesons and electrons from bottom decays produced in central Au+Au collisions to the binary-scaled production rate in peripheral Au+Au ( $R_{\rm CP}$ ) or minimum-bias p+p collisions ( $R_{\rm AA}$ ). Current measurements using non-photonic electrons as a measure of the abundance of charm and bottom hadrons indicate that the energy loss for heavy quarks is unexpectedly high and inconsistent with our current understanding of pQCD models. Based on the non-photonic electron data the theory of heavy quark energy loss is uncertain and may be completely wrong, especially with regards to bottom. The ability to separate and identify charm and bottom contributions is of crucial importance for such measurements. In this document we put emphasis on the charm sector because of the unique HFT capabilities in fully reconstructing the charm decays. From a physics point of view the bottom hadrons are equally important. It is important to point out that the bottom contribution can be determined only once the total charm contribution has been measured.

Another important study to be made with the HFT is a measurement of the elliptic flow of D-mesons down to very low  $p_T$  values. It is generally accepted that elliptic flow is established in the early partonic phase. If charm quarks, with a mass much larger than the temperature of the system, undergo elliptic flow then it has to arise from many collisions with the abundant light quarks. Thus, flow of charm quarks can be taken as a probe for frequent re-scatterings of light quarks and is an indication of thermalization that may be reached in the early stages of heavy ion collisions at RHIC. We believe that proof of thermalization constitutes the last step in the characterization of the strongly interacting matter created at RHIC. These important measurements require a very thin detector to push the measurement down to very low transverse momenta where elliptic flow is manifest.

Without the HFT upgrade the STAR experiment will not be able to execute the comprehensive heavy flavor program proposed here. However, STAR has been able to complete some initial charm measurements with the TPC alone, and with the data from the recent Run-7 STAR might be able to make limited progress towards an initial estimate for the B-meson contribution to the spectrum of the non-photonic electrons in Au+Au collisions.

The complete physics case for the HFT has been presented in the HFT proposal<sup>4</sup> and has been vetted in the HFT Science Review. In this Conceptual Design Report we will present the physics capabilities of the HFT in terms of low  $p_T$  charm, charm flow, charm suppression, as well as results obtained since the CD-0 review on  $\Lambda_C$  measurements, and the capability to study bottom production. The charm flow and charm suppression have been presented in detail already in the original proposal. Here we will present a brief summary of these two items and concentrate on the low  $p_T$  charm as well as  $\Lambda_C$  and B meson reconstruction capabilities.

# 2.1. Analysis Procedure

We start with a brief outline of our simulation procedures that are common to all results presented here. Details can be found in the HFT proposal.<sup>4</sup> The simulations presented here are performed (or updated) using an environment incorporating a simplified but up-to-date detector configuration (unless otherwise noted). Fast simulators have been used for PXL, IST, and SSD detectors, while a slow simulator has been used to simulate the TPC response. In all cases we use Au+Au events at 200 GeV.

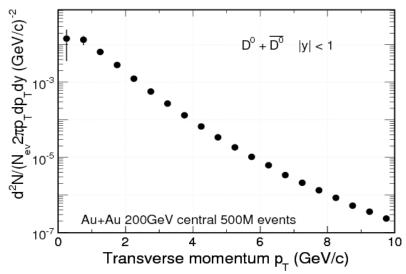

We used 10 k central Hijing Au+Au events as the basic environment where particles under study (e.g.  $D^0$ ,  $\Lambda_C$  and B mesons) are embedded in each event. These 'vanilla' events were also used to estimate the background. For  $D^0$  production we made the conservative assumption of a charm

yield of dN/dY = 0.002 per binary collision, about half the cross-section measured by STAR.<sup>5</sup> The events were produced in the standard STAR geometry, simulation and tracking environment. A new beam pipe with a radius of 2 cm and a thickness of 0.0762 cm was used. The PXL pile-up hit density corresponds to the expected RHIC-II luminosity (50\*10<sup>26</sup> cm<sup>-2</sup>s<sup>-1</sup>).<sup>6</sup> The beam diamond was assumed to be 0.01 cm in X-Y and a conservative 20 cm in Z with a Gaussian distribution. In the simulations we only generated events within ±5 cm from the detector center in Z direction in order to increase their usefulness. This constraint of the event vertex position is experimentally feasible at the L0 trigger level. Such a cut is absolutely necessary during data taking in order to ensure PXL hits for the decay products of heavy flavor. Minimum-bias event rates are not affected by this constraint, only high p<sub>T</sub> electron triggered ("High Tower" trigger in the electromagnetic calorimeter) event rates are affected. For a realistic beam-diamond size of about 15 cm this will reduce the useful event rates by about a factor of two.

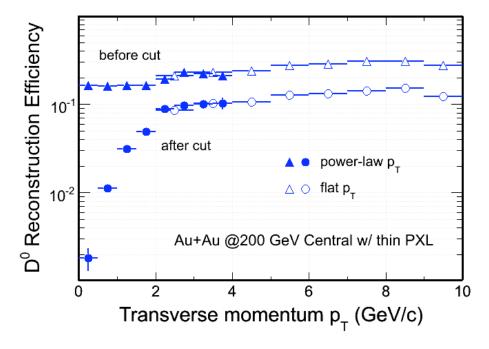

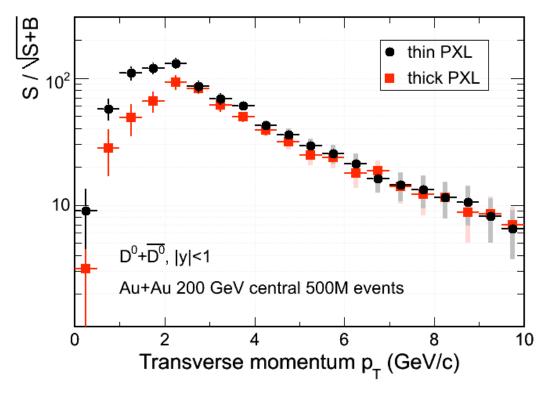

In order to study the effects of detector thickness, we simulated two cases. The "thin" configuration has a PXL thickness of 0.32% of a radiation length  $(X_0)$  and an IST thickness of 1.32%  $X_0$ . In this configuration the PXL thickness is slightly lower than that of the current design with 0.37%  $X_0$ . The "thick" configuration (PXL = 0.62%  $X_0$  and IST = 2.32%  $X_0$ ) explores the effect of roughly doubling the PXL and IST thicknesses. The "thick" detector is purely a hypothetical scenario, an extreme case used in these studies and it is a gross overestimate of any current alternative design.

## 2.2. $D^0$ Mesons

For the charm studies 5  $D^0$  were embedded in each Hijing event with 100% branching ratio (BR) decay to the channel  $D^0 \to K^- + \pi^+$  (the measured BR is 3.83%). In order to have good statistics at high  $p_T$ , the embedded  $D^0$   $p_T$  was input as a flat distribution. At low  $p_T$  (< 3.5 GeV/c), a power-law distribution with input parameters of  $<p_T>=1$  GeV/c and n=11 was used as the input  $D^0$  distribution to reduce the statistical error of the efficiencies. The pseudo-rapidity distribution was generated flat in  $\pm 1$  unit and also flat in azimuth. The daughter particles (K and  $\pi$ ) were identified via selection of the square of the mass distribution ( $m^2$ ) provided by the Barrel Time-of-Flight detector (TOF) with 100 ps timing resolution. A new geometry, a more realistic particle identification procedure and a more accurate background estimate are the main improvements since the CD-0 presentations.

The  $D^0$  was reconstructed with the same topological cuts as those in CD-0 so that the results could be compared to each other. Figure 1 shows the topology of a  $D^0$  decay and Table 1 gives the values of the specific cut-set used in reconstruction. This is an adequate set for these studies but it is not fine-tuned; studying the experimental distributions will do this. Additional TOF  $m^2$  cuts were applied at low  $p_T$  (< 3 GeV/c) for K- $\pi$  identification. Tracks with large  $m^2$  were rejected as protons. At high  $p_T$  (> 3 GeV/c), K and  $\pi$  cannot be separated, so the only  $m^2$  cut applied is for proton rejection. Effects of the K- $\pi$  misidentification are included in the simulation.

Figure 2 shows two examples of expected invariant mass distributions at low (left panel) and high (right panel) transverse momentum values. Both plots are extrapolations to 500 M events based on the analysis of our 10 K event sample after proper scaling. Only statistical errors are shown. For the specific set of cuts one sees that the lower  $p_T$  distributions are high in combinatorial background mainly due to multiple scattering. The reconstruction to as low  $p_T$  values as possible will allow the precise determination of charm cross-sections using minimal extrapolation factors while integrating over  $p_T$  and the precise knowledge of spectra at intermediate and low  $p_T$  will allow for a precise determination of bottom contributions and flow measurements of both flavors.

Figure 1: Topology of D<sup>0</sup> decay and cut variable definition.

| Cuts                  | D°                      |

|-----------------------|-------------------------|

| TPC hits              | > 15                    |

| Pseudo-rapidity range | ± 1.0                   |

| PIXEL hits            | 2                       |

| DCA (primary vertex)  | ≥ 50 µm                 |

| $DCA_{\pi K}$         | ≤ 50 μm                 |

| $\cos (\theta)$       | ≥ 0.98                  |

| Δm                    | ≤ 35 MeV/c <sup>2</sup> |

Table 1: The set of cut values used for D<sup>0</sup> reconstruction.

The  $D^0$  reconstruction efficiency in Au+Au central collisions is shown in Figure 3. The filled symbols represent the efficiencies extracted with power-law distributed embedded  $D^0$ , whereas the open circles are for an embedded flat  $D^0$   $p_T$  distribution. The triangles show the fraction of the decays where both daughter tracks were successfully reconstructed in the system. We also required that both tracks had two hits in the PXL detector. This represents the upper limit for signal reconstruction efficiency. The circles show the fraction of the reconstructed decays after our set of cuts has been applied to reduce background to acceptable levels. This latter curve depends strongly on the choice of cuts. Above 2 GeV/c the  $D^0$  efficiency is of the order of 10% (remember that the branching ratio for this specific decay channel is not included in this number). Below 2 GeV the efficiency rapidly drops to 0.1% at about 500 MeV/c transverse momentum.

Figure 2: Estimated  $D^0$  invariant mass distributions for two  $p_T$  intervals. The estimate was based on simulations with 10 K events and depends on the specific values of reconstruction cuts.

Figure 3:  $D^0$  reconstruction efficiency as a function of  $p_T$ . Filled symbols are for a power law input distribution and open symbols are for a flat (in  $p_T$ ) input distribution.

For the calculation of the signal significance the reconstructed  $D^0$  signal was scaled to match the expected  $D^0$  production yield times the branching ratio per central Au + Au collision. The distribution of the background was scaled to the expected background level by taking into account sources such as random combinations, particle misidentification and high  $p_T$  proton contamination. Due to small statistics and large fluctuations of the Hijing background at high  $p_T$ , we used an exponential function to extrapolate the background shape to empty bins at higher  $p_T$ .

The difference of the background shape while varying the cuts was used as a tool to estimate systematic uncertainties.

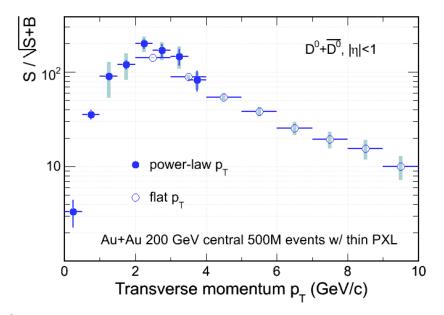

Figure 4 shows the signal significance distributions for the PXL with flat  $p_T$  (open circles) and with power-law  $p_T$  (filled circles). The systematic errors are estimated from the difference of the background shape by varying cuts. The power-law  $p_T$  distribution was used to more realistically simulate the statistical errors at low  $p_T$ . We see clearly the capability to measure  $D^0$  as low  $p_T$  as 0.5 GeV/c, a value well below the expected mean  $p_T$  value of about 1 GeV/c. With the HFT we will be able to very accurately determine the total charm cross-section and spectra with minimal extrapolations. Since our simulation sample is limited (10K events), all error bars shown in the following figures are statistical only and based on the values shown in this figure. Background fluctuations could contribute another factor of up to about sqrt(2) but those cannot be adequately simulated in this small sample.

Figure 4:  $D^0$  reconstruction significance as a function of  $p_T$ . Filled circles are for a power law distribution and open circles are for a flat distribution.

Figure 5 shows the anticipated  $D^0$   $p_T$  spectrum. Notice the broad range of  $p_T$  reach and the expected accuracy of the points. This sample is expected to be the result of a single year's run (about 6 months of RHIC running). We observe that we can achieve good signal significance for a wide range of transverse momentum values, starting almost at zero  $p_T$  (a realistic cut off value for an acceptable S/N ratio is around 300 MeV/c). Our simulation procedure is not yet optimized. For example all the cuts used so far are fixed pT cuts. Consequently, all our estimates represent lower limits for efficiencies. Initial studies suggest that by using pT dependent cuts, e.g. through the use of Support Vector Machines, gains in efficiency at low pT can be realized. In the following (unless otherwise noted) we use the thin PXL configuration as the default one.

## 2.3. Performance of Alternate Configurations

As part of our work addressing questions from the CD-0 Review we have addressed several hypothetical scenarios or risk factors. Two of those are presented here as supplementary material to document those results.

One risk factor refers to the case where either the IST or SSD sustains a catastrophic failure and are not available. Studies have shown that charm physics will not be possible with the existing tracking algorithms in the case where both detectors fail.

Figure 5: Estimated statistical accuracy for reconstructed  $D^0$  spectra. Errors shown are statistical only.

The second scenario is rather technical and it has to do with the PXL layer thickness. In our studies we simulated two thickness scenarios that differ by a factor of two in order to get a feeling for the system performance as a function of layer thickness.

#### 2.3.1. System Performance without SSD or IST

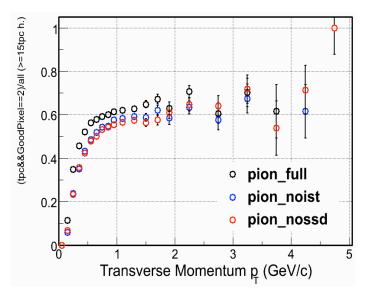

We performed simulations where either the entire SSD or the entire IST detector was not functional, i.e. the hit information was not available to the tracking packages. The impact on physics observables of this scenario comes exclusively through its modification of the overall system tracking efficiency, since the PXL layers primarily determine the pointing accuracy of HFT. The results are shown in Figure 6 (full simulation) as the single-track reconstruction efficiency for pions. The black points show the efficiency of the full system, the blue points the efficiency in the case of dead-IST and the red points the efficiency for dead-SSD.

As we analyze the results we should keep in mind that one of the design goals of HFT was to have built-in redundancy in tracking just for this case, i.e. the failure of a critical, intermediate tracking layer. The simulation shows that for the no-SSD case we suffer an average loss of efficiency of about 5-8% depending on p<sub>T</sub>. For the no-IST case the number is similar, i.e. the detectors can act as a backup of each other. By squaring the absolute single track efficiency in the various cases, as obtained by the full simulations, we can estimate the expected loss of signal

(D<sup>0</sup>) efficiency, which turns out to be about 5% on the average *absolute* efficiency loss or about 20% relative loss (from  $\sim$ 25% to  $\sim$ 20%).

On top of this efficiency loss we also expect a slight increase of the background levels, since any single track inefficiency results in an increased rate of ghost tracks. This level is expected to be minimal after the selection software cuts are applied. Full simulation studies showed that the level of ghost tracks (before cuts) increases by 0-10%, depending on p<sub>T</sub>. Therefore the impact on the S/N is expected to be minimal. We conclude that the loss of an entire layer of the intermediate tracking system has a sizeable impact on the system performance but, until repairs are done, the key physics measurements could be carried out. As a final note on this subject let us remember that this failure analysis used the tracking software without any modifications. In real-life, tracking optimization techniques will be deployed in order to clean up and recover part of the lost efficiency; therefore what is presented here is a rather extreme, pessimistic scenario.

Figure 6: Single track reconstruction efficiency for the full HFT (black), the HFT without the IST (blue) and the HFT without the SSD (red) points.

#### 2.3.2. System Performance for two PIXEL Thicknesses

Our original simulations were carried out using a radiation length of 0.28% for the first pixel layer and a radiation length of 0.14% for the beam pipe. Here we address the physics risk due to increases in the radiation length. The important parameter to be examined is the impact parameter of the pixel detector. The impact parameter resolution (accuracy of pointing to the vertex) can be expressed in the following form:

$$\sigma^{2} = \frac{\sigma_{1}^{2} r_{2}^{2} + \sigma_{2}^{2} r_{1}^{2}}{(r_{2} - r_{1})^{2}} + \frac{\theta_{mcs}^{2} r_{1}^{2}}{\sin^{2}(\theta)}$$

where  $\sigma 1$  and  $\sigma 2$  are the position resolutions on each detector layer, r1 is the inner layer radius and r2 is the outer layer radius and  $\theta_{mes}$  is the multiple coulomb scattering angle in the first layer of the detector.  $\theta$  is the angle of entrance into the detector relative to the

beam line. The second term, the projection error due to the multiple coulomb scattering, is the parameter of interest and it is this term that dominates the detector performance. The multiple coulomb scattering angle is given as:

$$\theta_{mcs} = \frac{13.6 (MeV/c)}{\beta p} \sqrt{\frac{x}{X_0}}$$

where x/X0 is the fraction radiation length and represents the radiation length for both the inner pixel layer and the beam pipe. In this approximation the beam pipe is assumed to be at the same radius as the inner pixel detector layer. The original vertex projection resolution, which has been used for our simulations, is:

$$\sigma = 13\mu m \oplus \frac{22 \, GeV}{p \cdot c} \mu m$$

As the design of the ladder has matured the radiation length of the ladder has increased from 0.28% to 0.37%. This increase is the result of adding another carbon composite backing layer plus additional adhesive. This was necessary to maintain sufficient position stability (position stability affects the first term of the pointing resolution expression). The current ladder design has been extensively analyzed for position stability, so further design changes should not be necessary in order to meet the stability requirements. The greatest risk to increased ladder radiation length is the aluminum-Kapton cable. We have a vendor that should be able to produce an aluminum-Kapton cable, but aluminum-Kapton has traditionally been difficult, so there is the risk that we might have to use copper in place of the aluminum. If this is required the radiation length of the ladder will increase from 0.37% to 0.51%.

There was also an increase in the beam pipe thickness. The only manufacturer, Brush Wellman, was originally comfortable building a 0.5 mm beryllium beam pipe, but they have subsequently argued that 0.75 mm would be much less risky and less expensive. The degradations in the impact parameter resolution resulting from these various changes are summarized in Table 2. The last entry in the table is for a copper ladder cable. This is the worst case and results in a pointing resolution that is 32% worse than the original design which was simulated.

| Configuration | Beam                | Ladder | Impact parameter     | % resolution degradation |

|---------------|---------------------|--------|----------------------|--------------------------|

|               | pipe X <sub>0</sub> | $X_0$  | resolution, MCS term | over original            |

| original      | 0.14%               | 0.28%  | 22 GeV·µm/p·c        |                          |

| current with  | 0.23%               | 0.37%  | 26 GeV·μm/p·c        | 19%                      |

| aluminum      |                     |        |                      |                          |

| current with  | 0.23%               | 0.51%  | 29 GeV·μm/p·c        | 32%                      |

| copper        |                     |        |                      |                          |

Table 2: Summary of radiation length and impact parameter resolution. The original HFT PIXEL design is compared with the current ladder design and the worst-case example where the aluminum in the ladder cable is replaced with copper.

It should be noted that even with these increases the worst-case ladder radiation length is still less than 1/2 that of pixel detectors in ATLAS, ALICE or PHENIX.

Full system performance simulations (see Figure 7) show that increasing the radiation length of the first pixel layer from 0.32% to 0.62% reduces the significance factor by a factor of 2 in the  $p_t$  region around 0.5 GeV/c. Note this set of values are slightly different from the values discussed above ( 37% and 51%) but in the same general range.

The reduction in significance results in an increased data sample to achieve the same statistical uncertainty as specified in the following expression.

$$N = \frac{1}{U^2} \left( \frac{1}{s} + \frac{b}{s^2} \right)$$

N is the number of events required to achieve a signal measurement uncertainty U, s is the mean signal per event and b is the mean combinatoric background per event in the peak measuring window.

This mean that a factor of 4 increase in data is required for  $p_T$  less than 1.5 GeV/c to achieve the same statistical significance and to make up for the 30% increase in the radiation length of the first pixel layer. We can expect some improvement in this increase by optimizing the cuts. The proposal statistics is based on 500M events. It is plausible to collect twice that statistics in a 10 week Au+Au run. It might require additional computing resources over what is currently projected to be available, so careful planning and revisiting software will be called for. Design improvements in the ladder flexible cable are under study, which could result in fewer layers. This could restore the ladder radiation length to 0.3% while still using copper conductors.

Figure 7: A measure of the significance factor from simulation for the PXL layer with a radiation length of 0.32% and 0.62%.

#### 2.4. Charm Flow

At RHIC partonic collectivity has been well established via the measurements of hadrons containing light quarks (u, d, and s). Recent v<sub>2</sub> results from multi-strange hadrons, phi mesons and Omega baryons, further confirm this important discovery.<sup>7</sup> Charm quarks are abundantly produced at RHIC energies. Due to their high mass and small interaction cross-section, the strength of elliptic flow of heavy flavor hadrons may be a good indicator of thermalization occurring at the partonic level. If all quarks in heavy flavor hadrons flow with the same pattern as the quarks in the light flavor hadrons, this indicates frequent interactions between all quarks. Hence, thermalization of light quarks is likely to have been reached through partonic rescattering.

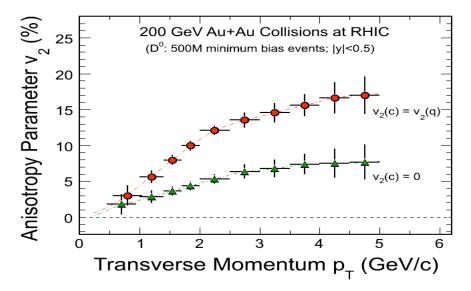

Figure 8 shows what precision in flow measurement can be reached with 500 M minimum-bias events taken in STAR with the HFT. The red points show expectations from a transport model<sup>8</sup> for the case that the charm quark has the same size partonic flow as measured for the light quarks. The green points show the limiting case where the charm quark has zero partonic  $v_2$ . A measurement close to the red points would mean that frequent rescattering has induced collectivity for the heavy quark, while a measurement close to the green points would indicate little partonic rescattering and thus no thermalization. Our measurement is expected to fall between those limits. It is obvious that the HFT will allow for a precision measurement that will shed light on the question of thermalization.

Figure 8: Precision projections of the  $v_2$  measurement as a function of  $p_T$  for the case where charm flows the same way as light quarks (red) and for the case where charm does not flow (green).

## 2.5. Heavy Quark Energy Loss

The discovery of a factor of 5 suppression of high  $p_T$  hadrons (5 <  $p_T$  < 10 GeV/c) produced in Au+Au collisions at RHIC and the disappearance of the away-side jet has been interpreted as evidence for jet quenching. This effect was predicted to occur due to radiative energy loss of high energy partons that propagate through a dense and strongly interacting medium. The energy loss of heavy quarks is predicted to be significantly less compared to light quarks because